A Thesis for the Degree of Ph.D. in Engineering

### Design of High Efficiency Monolithic Switched-Capacitor DC-DC Converters for IoT Applications

January 2024

Graduate School of Science and Technology Keio University

Tan Yi

### Committee Members:

Hiroki Ishikuro Cheng Huang Nobuhiko Nakano Makoto Takamiya Kentaro Yoshioka

### Abstract

Switched capacitor power converter circuits are very common in Power Management Integrated Circuits (PMICs) in modern devices because of the favorable high integrity provided by on-chip capacitors. Recently, with the development of Internet-of-Things (IoT), the limited power sources have brought a series of new challenges to switched capacitor power converters.

On the one hand, using the energy harvester as a supplementary power source can extend the maintenance intervals for sensor nodes. However, the lower power harvested from the environment results in a low closed-loop voltage of the generator, raising design challenges in achieving high power conversion efficiency for energy-harvesting PMICs. On the other hand, because of the long standby times and high power consumption in the active state, designers aim for high power conversion efficiency of PMICs under different loading conditions and fast transient response to ensure sensor system availability while minimizing delays, which presents challenges for controller design.

Therefore, this research focuses on the low-power optimization of switched capacitor power converters. Using the thermoelectric energy harvester as an example, we will introduce our efforts to optimize transistor performance under ultra-low power and low voltage conditions, enhancing the peak efficiency achievable by existing topologies. Additionally, we will demonstrate dual lower-bound hysteretic control that provides efficient operation over a wide output power range. Therefore, the proposed techniques are expected to improve the overall performance of generic SCPC converters in IoT applications.

## Contents

| A | bstra | ct      |                                                            | i  |

|---|-------|---------|------------------------------------------------------------|----|

| 1 | Intr  | oductio | on.                                                        | 1  |

| 2 | Cha   | llenge  | s in Always-On IoTs System                                 | 8  |

| 3 | Effi  | ciency  | Optimization in Low Voltage Low Power Applications         | 13 |

|   | 3.1   | Trade   | -offs in SCPC Design                                       | 14 |

|   |       | 3.1.1   | Conduction Losses                                          | 14 |

|   |       | 3.1.2   | Impact of Slow and Fast Switching Limit in Conduction Loss | 15 |

|   |       | 3.1.3   | Switching Losses                                           | 17 |

|   |       | 3.1.4   | Trade-offs in Low Voltage Low Power Applications           | 19 |

|   | 3.2   | Gate V  | Voltage Optimization for Target $R_{on}$                   | 21 |

|   |       | 3.2.1   | Gate Voltage Optimization in Strong Inversion Region       | 21 |

|   |       | 3.2.2   | Gate Voltage Optimization in Weak Inversion Region         | 24 |

|   |       | 3.2.3   | Numerical Calculation                                      | 26 |

|   |       | 3.2.4   | Comparsion with Dynamic Body Biasing                       | 31 |

|   |       | 3.2.5   | Summary of Methodology                                     | 34 |

|   | 3.3   | Imple   | mentation and Verficiation                                 | 35 |

|   |       | 3.3.1   | Verficiation Circuits                                      | 35 |

|   |       | 3.3.2   | Controller                                                 | 39 |

|   |       | 3.3.3   | Startup Process                                            | 41 |

|   |     | 3.3.4  | Measurement Results                                     | 42 |

|---|-----|--------|---------------------------------------------------------|----|

|   |     | 3.3.5  | Comparison of Performance                               | 47 |

|   | 3.4 | Discus | ssions                                                  | 48 |

| 4 | Dua | l Lowe | er-Bound-Hysteresis Control                             | 50 |

|   | 4.1 | Conce  | ept Circuit                                             | 52 |

|   |     | 4.1.1  | Model of Transient Behavior in SCPC                     | 52 |

|   |     | 4.1.2  | Behavior Analysis of the Proposed DLBHC Control         | 55 |

|   |     | 4.1.3  | DLBHC and Frequency Control Design                      | 57 |

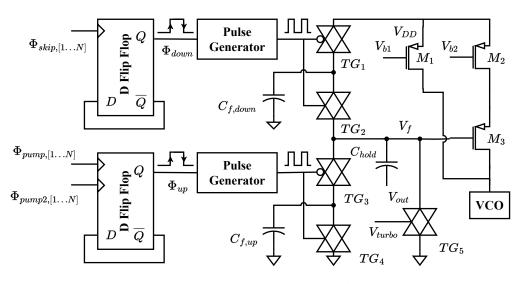

|   |     | 4.1.4  | Frequency Controller Design                             | 59 |

|   | 4.2 | Mode   | l for Delay Time Design                                 | 61 |

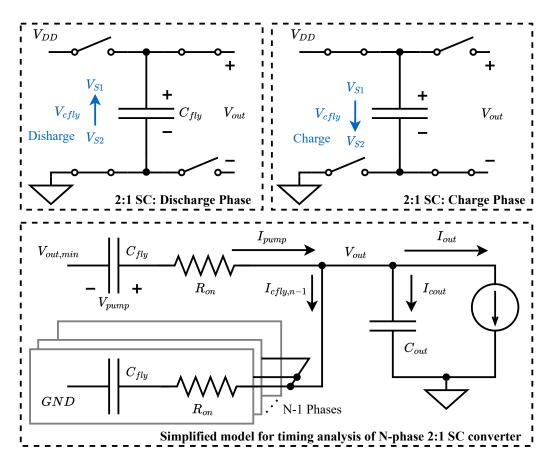

|   |     | 4.2.1  | Simplified Model for Timing Design                      | 61 |

|   |     | 4.2.2  | Light-load DLBHC Timing Analysis                        | 64 |

|   |     | 4.2.3  | Heavy-load DLBHC Timing Analysis                        | 67 |

|   |     | 4.2.4  | Impact of Transistor Resistance Mismatch                | 67 |

|   |     | 4.2.5  | Simulation Based Analysis Verification                  | 68 |

|   |     | 4.2.6  | Discussion on $T_D$ Selection for DLBHC Design          | 72 |

|   | 4.3 | Imple  | mentation with Distributed Multi-Phase DLBHC Controller | 73 |

|   |     | 4.3.1  | Distributed Multi-Phase DLBHC Design                    | 73 |

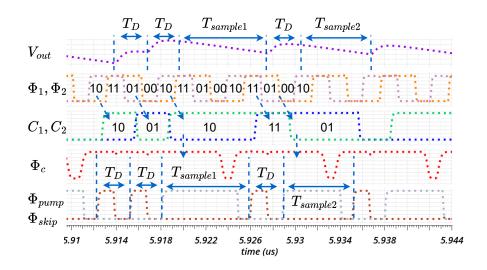

|   |     | 4.3.2  | Simulated Transient Behavior of Proposed Design         | 76 |

|   |     | 4.3.3  | Measurement Result                                      | 78 |

|   | 4.4 | Imple  | mentation with Centralized Multi-Phase DLBHC Controller | 86 |

|   |     | 4.4.1  | Circuit Design                                          | 86 |

|   |     | 4.4.2  | Delay Compensations                                     | 86 |

|   |     | 4.4.3  | Centralized DLBHC with Delay Compensation               | 91 |

|   |     | 4.4.4  | Dual-Mode Operations                                    | 91 |

|   |     | 4.4.5  | Frequency Control Design                                | 92 |

|                  |                                   | 4.4.6 Measurement Results | 92  |

|------------------|-----------------------------------|---------------------------|-----|

|                  | 4.5 Comparison of the Performance |                           |     |

|                  | 4.6                               | Discussions               | 99  |

| 5                | Con                               | clusion                   | 100 |

| Ac               | knov                              | vledgements               | 102 |

| Bibliography 103 |                                   |                           |     |

# **List of Figures**

| 1.1 | Statistic and prediction of the number of connected devices from IoT           |    |

|-----|--------------------------------------------------------------------------------|----|

|     | Analytics [1] and Statista [2]                                                 | 2  |

| 1.2 | Typical PMIC system in IoT devices.                                            | 3  |

| 1.3 | Example of Step Down PMIC: SIPC, SCPC and Hybrid Converters                    | 4  |

| 1.4 | Typical SCPC converters comparison.                                            | 5  |

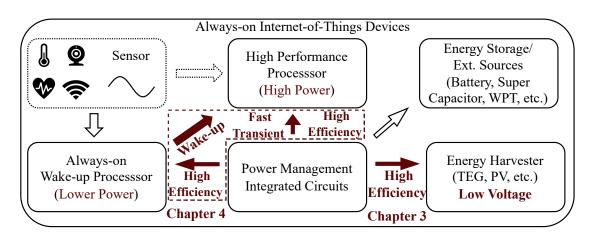

| 2.1 | Challenges in Always-on IoT devices addressed by this thesis: en-              |    |

|     | ergy harvesting (Chapter 3), standby efficiency and wake-up speed              |    |

|     | (Chapter 4)                                                                    | 9  |

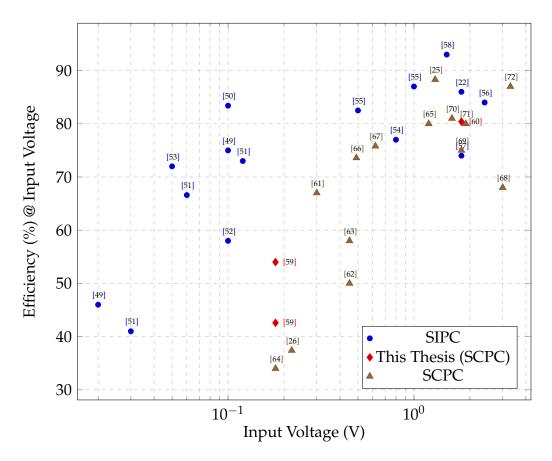

| 2.2 | Review of PMIC performance: efficiency vs input voltage                        | 10 |

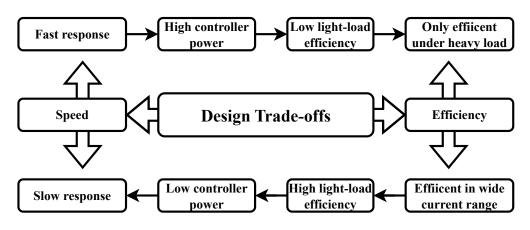

| 2.3 | Design Trade-offs in the controller design                                     | 11 |

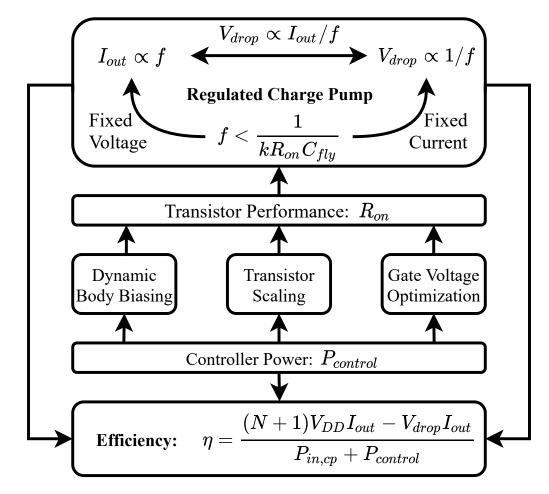

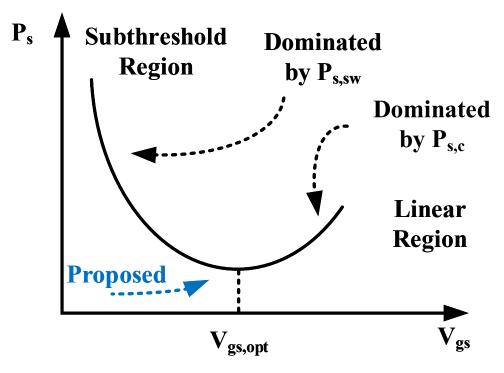

| 3.1 | Charge pump design trade-offs                                                  | 20 |

| 3.2 | Conceptual graph of optimum gate voltage                                       | 24 |

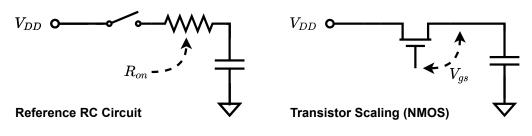

| 3.3 | Circuit setup for evaluating the transistor scaling under different $V_{gs}$ . | 26 |

| 3.4 | Extraction of the $V_{th}$ from simulation results                             | 27 |

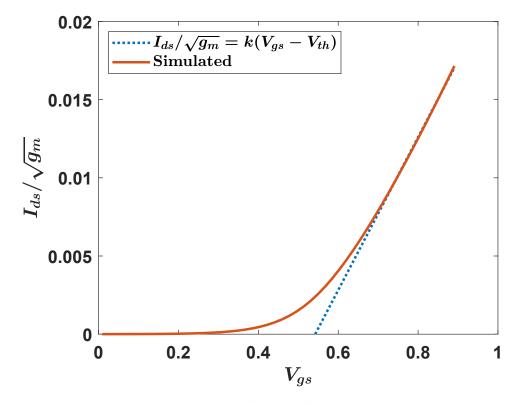

| 3.5 | Verification of the theory when $R_{on} = 3000\Omega$                          | 28 |

| 3.6 | Verification of the theory when $R_{on} = 200\Omega$                           | 29 |

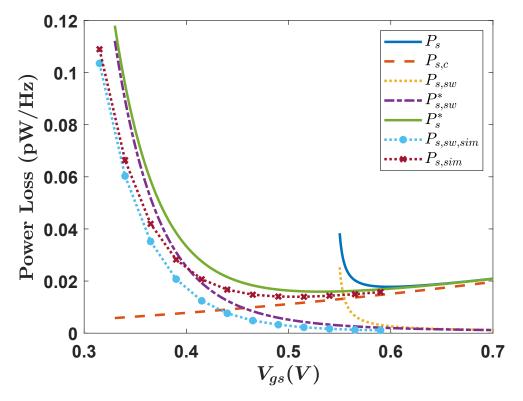

| 3.7 | Optimum gate voltage at different $R_{on}$ and $C_c$                           | 30 |

| 3.8 | Power losses at optimum gate voltage with different $R_{on}$ and $C_c$         | 31 |

| 3.9 | (a) Circuit setup of typical charge pumps with DBB. (b) Setup of gate          |    |

|     | voltage optimization for simulations. (c) Setup of DBB for simulations.        | 32 |

| 3.10 | Comparison between dynamic body biasing and gate voltage opti-      |    |

|------|---------------------------------------------------------------------|----|

|      | mization                                                            | 33 |

| 3.11 | The general consideration of determining the optimum gate voltage.  | 34 |

| 3.12 | Charge pump structure.                                              | 36 |

| 3.13 | (a) Charge pump structure. (b) $V_{gs}$ in different stages         | 36 |

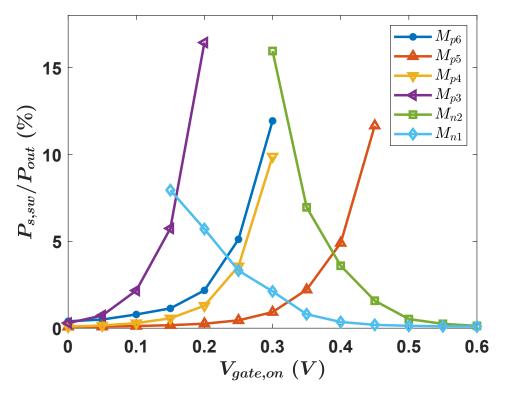

| 3.14 | Minimal $P_{s,sw}$ of each stage at different $V_{gate,on}$         | 37 |

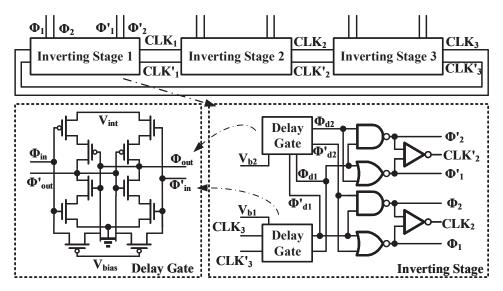

| 3.15 | Controlled oscillator.                                              | 39 |

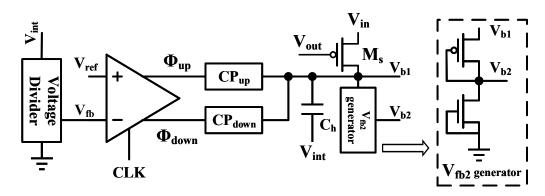

| 3.16 | Feedback loop for $V_{fb1}$ and $V_{fb2}$ generation                | 40 |

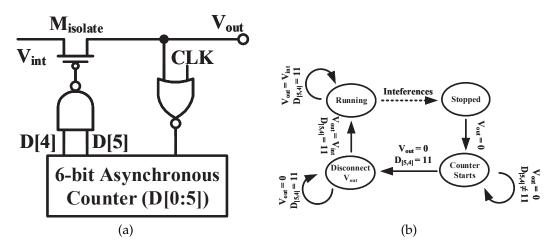

| 3.17 | (a) Startup circuit (b) Startup process                             | 40 |

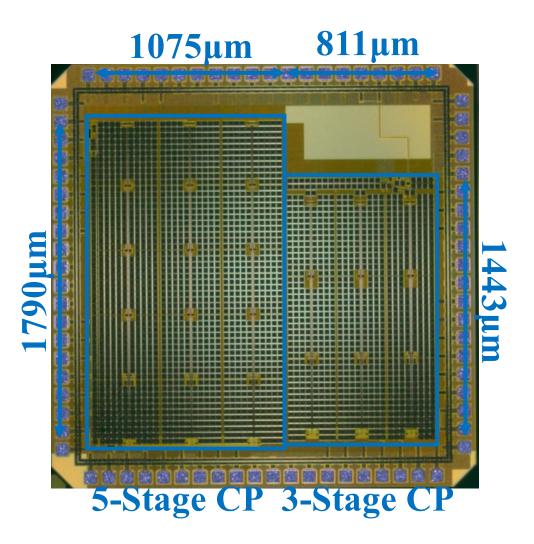

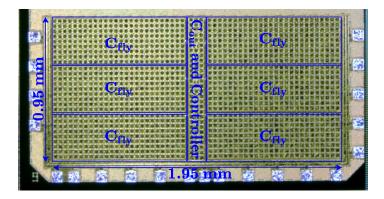

| 3.18 | Chip micrograph                                                     | 43 |

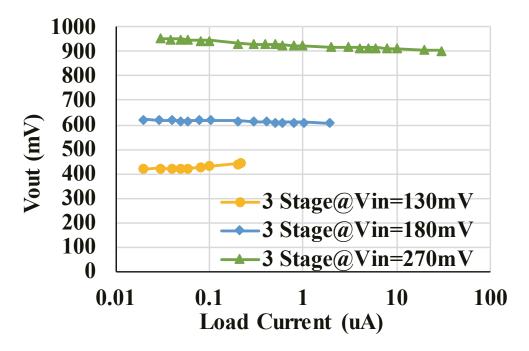

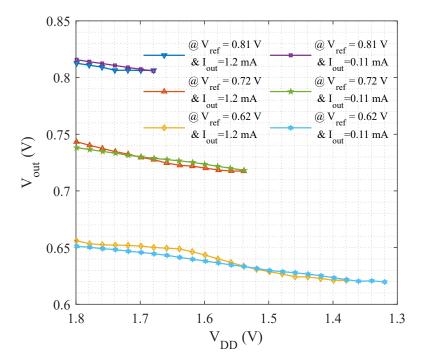

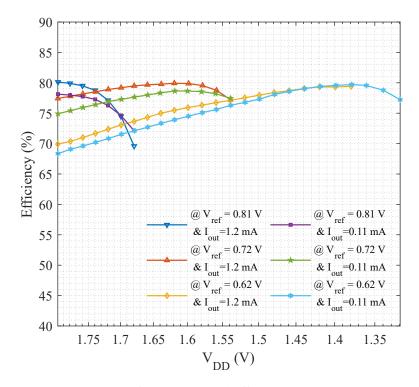

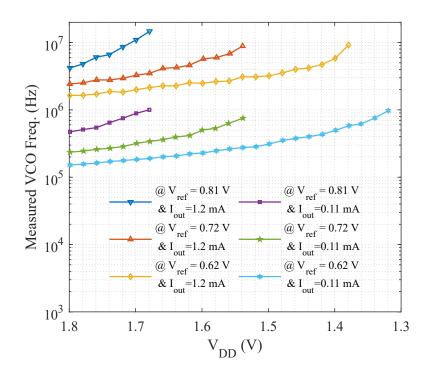

| 3.19 | Load regulation of proposed 3-stage charge pump                     | 44 |

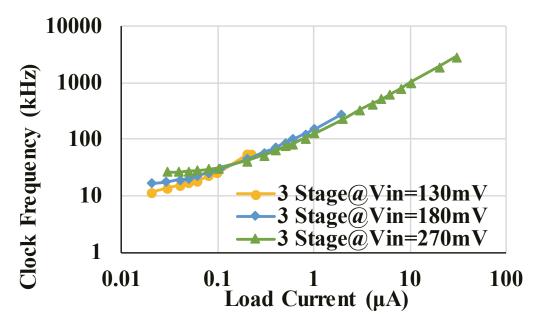

| 3.20 | Clock frequency of proposed 3-stage charge pump                     | 44 |

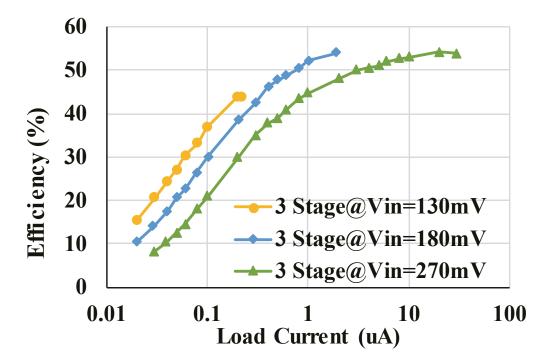

| 3.21 | Efficiency of proposed 3-stage charge pump                          | 45 |

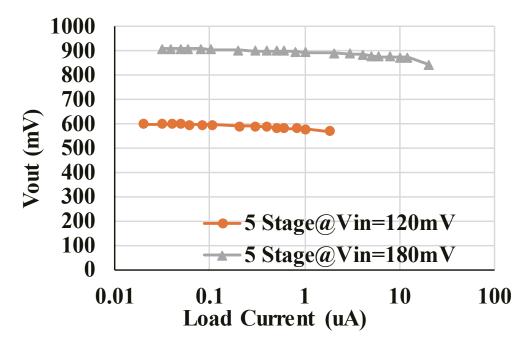

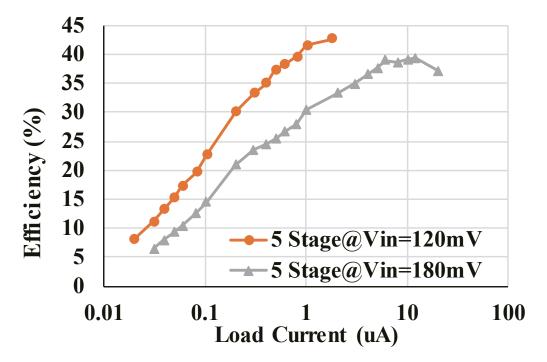

| 3.22 | Load regulation of proposed 5-stage charge pump                     | 45 |

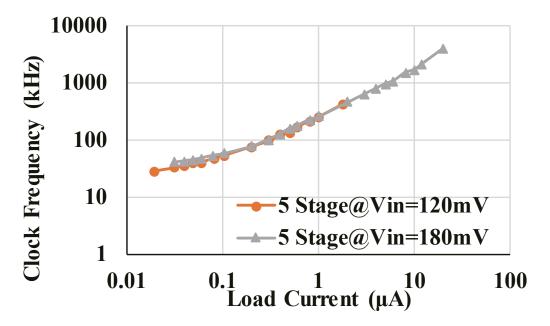

| 3.23 | Clock frequency of proposed 5-stage charge pump                     | 46 |

| 3.24 | Efficiency of proposed 5-stage charge pump                          | 46 |

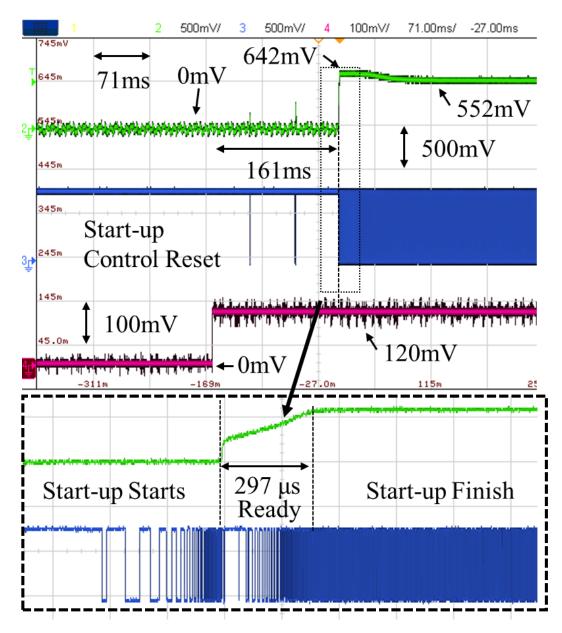

| 3.25 | Startup Measurement.                                                | 47 |

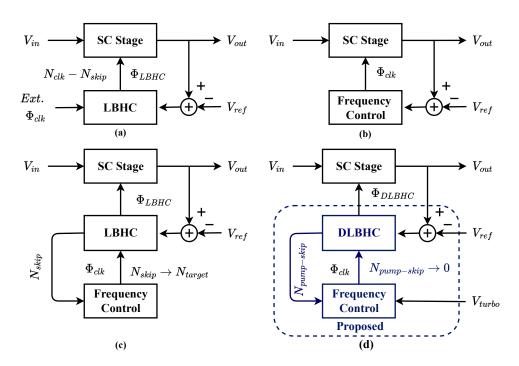

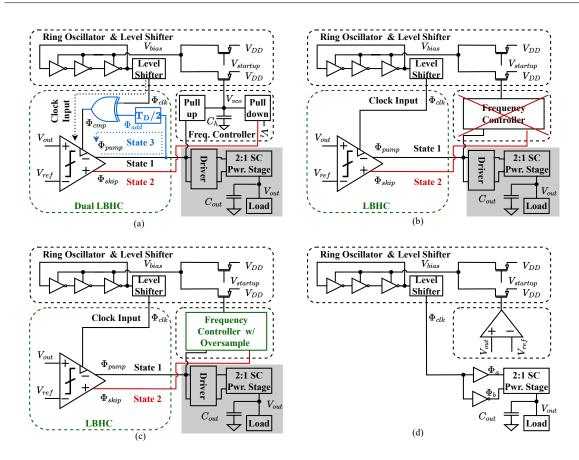

| 4.1  | SC converters based on (a) LBHC, (b) frequency control, (c) LBHC SC |    |

|      | converter with pulse skipping based frequency control [3], and (d)  |    |

|      | proposed design.                                                    | 51 |

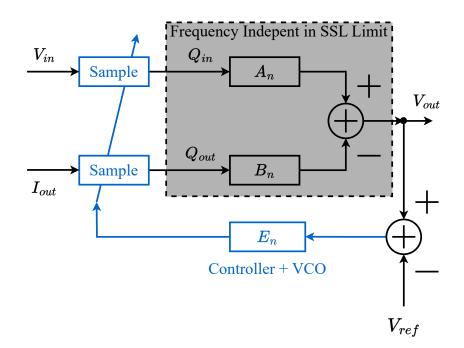

| 4.2  | Model of the SCPC with Frequency Control.                           | 53 |

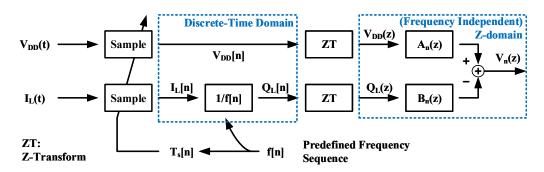

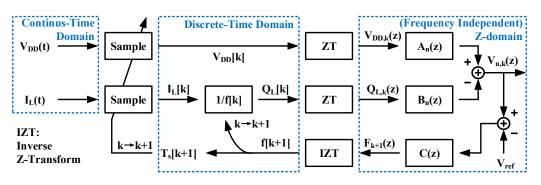

| 4.3  | Open-loop charge pump in the mixed domain                           | 54 |

| 4.4  | Closed-loop charge pump with synchronized controller                | 54 |

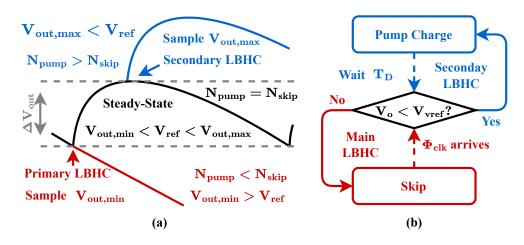

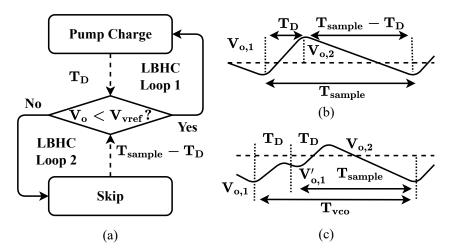

| 4.5  | (a) Illustration of the proposed DLBHC control (b) flow chart       | 56 |

| 4.6  | Comparison between open loop DLBHC and LBHC, assuming a heavy       |    |

|      | load                                                                | 56 |

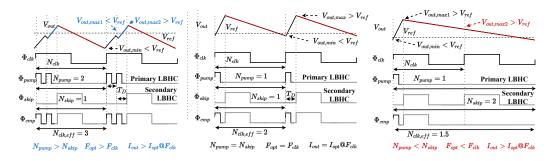

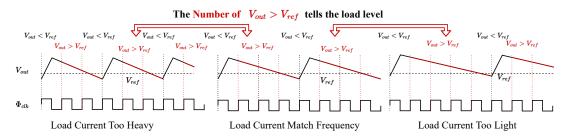

| 4.7  | Operation of DLBHC in open-loop: (left) heavy load, (middle) opti-               |    |

|------|----------------------------------------------------------------------------------|----|

|      | mum Load, (right) light load.                                                    | 56 |

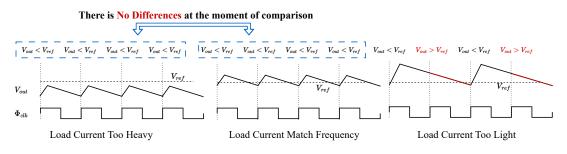

| 4.8  | Operation of LBHC in open-loop: (left) heavy load, (middle) opti-                |    |

|      | mum Load, (right) light load.                                                    | 57 |

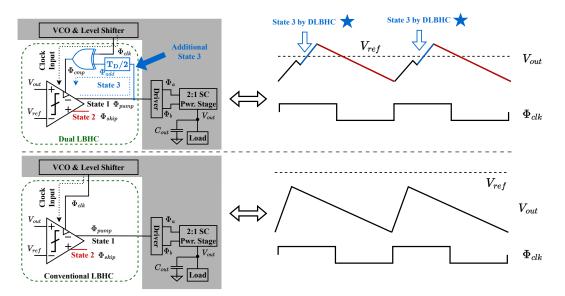

| 4.9  | Comaprsion of different conceptual implementations w/ frequency                  |    |

|      | control (a) proposed DLBHC, (b) LBHC, frequency control is not prac-             |    |

|      | tical, (c) oversample based LBHC [3] (d) frequency control w/ error              |    |

|      | amplifier                                                                        | 59 |

| 4.10 | Operation of Oversampled LBHC in open-loop: (left) heavy load,                   |    |

|      | (middle) optimum Load, (right) light load                                        | 59 |

| 4.11 | Frequency controller design.                                                     | 61 |

| 4.12 | Modeling for the analysis of an N-phase 2:1 SC converter                         | 62 |

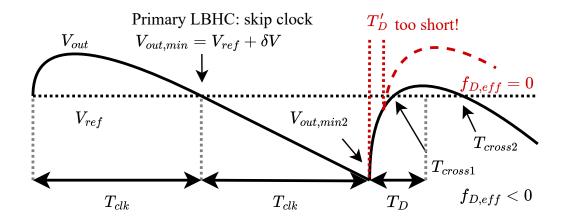

| 4.13 | DLBHC operations: proper $T_D$ (black) and inproper $T_D$ (red)                  | 62 |

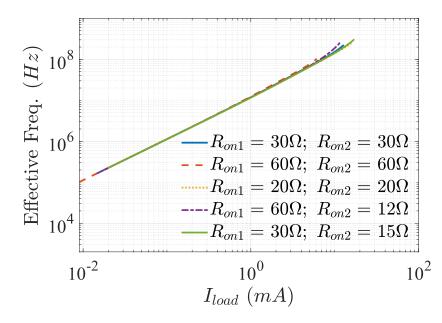

| 4.14 | Simulated relationship between steady-state $I_{load}$ and $f_{eff}$             | 68 |

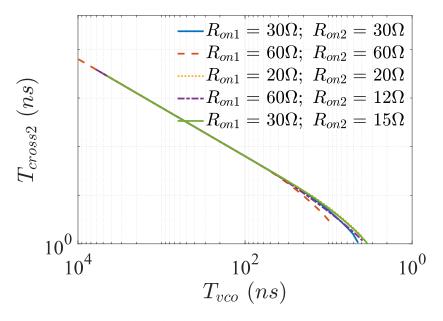

| 4.15 | Simulated relationship between $T_{cross2}$ and $T_{clk}$                        | 69 |

| 4.16 | Simulated relationship between $T_{cross2}$ and $T_{clk}$                        | 69 |

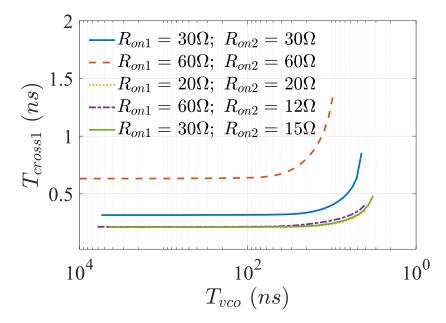

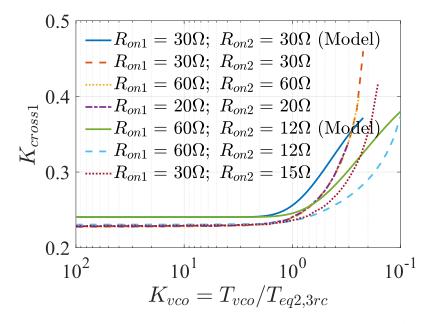

| 4.17 | Simulated relationship between $K_{cross1}$ and $K_{vco}$ (Simulation vs Model). | 70 |

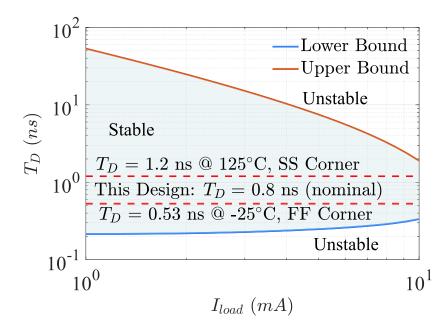

| 4.18 | Process and temperature variation of selected $T_D$ (1.8 V to 0.8 V)             | 70 |

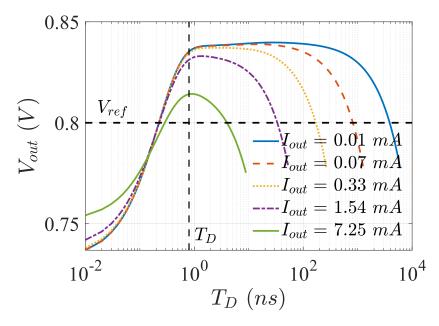

| 4.19 | Relationship between the sampled $V_{out}$ and $T_D$ during the transient        |    |

|      | recovery                                                                         | 71 |

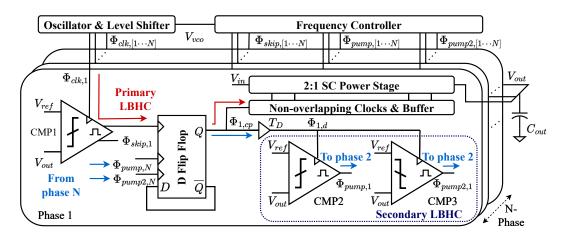

| 4.20 | System block diagram of the proposed N-phase DLBHC SC Converter.                 | 74 |

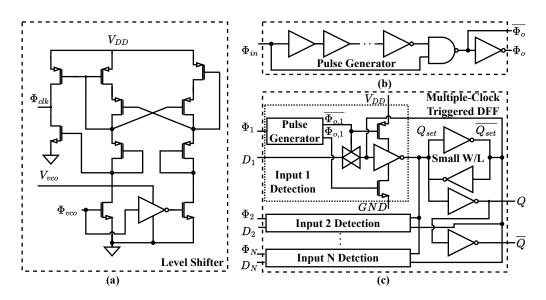

| 4.21 | Detailed circuits of (a) Level shifter (b) Pulse generator (c) Multiple-         |    |

|      | clock triggered DFF                                                              | 75 |

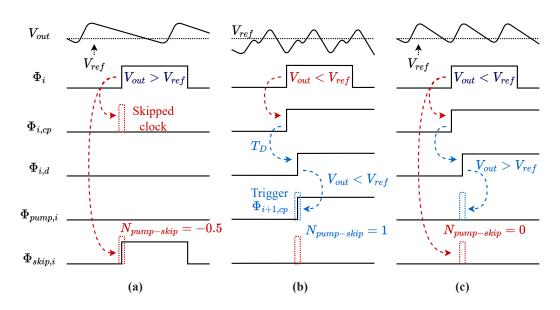

| 4.22 | Conceptual graph of DLBHC operations when (a) $f_{clk} = 2f_{opt}$ , (b)         |    |

|      | $f_{clk} = f_{clk}/2$ and (c) $f_{clk} = f_{opt}$ .                              | 76 |

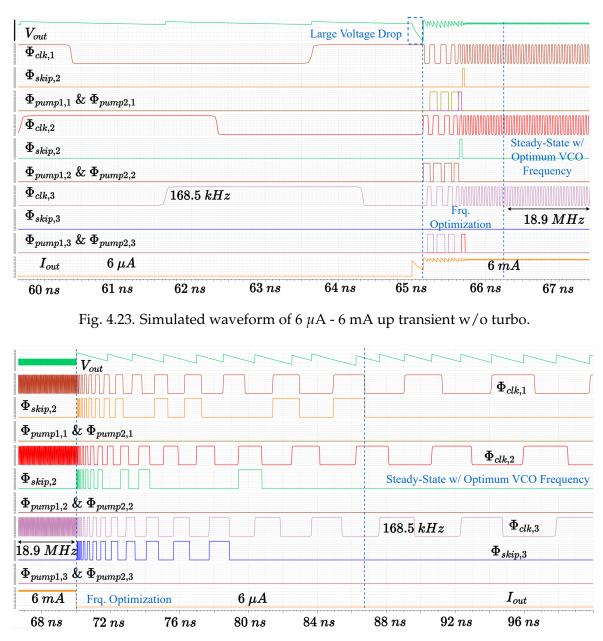

| 4.23 | Simulated waveform of 6 $\mu$ A - 6 mA up transient w/o turbo                    | 77 |

| 4.24 | Simulated waveform of 6 mA - 6 $\mu$ A down transient w/o turbo                  | 77 |

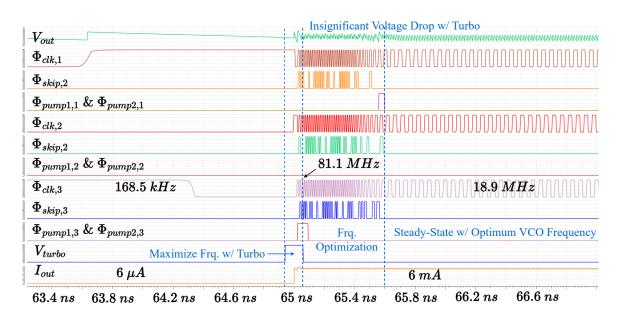

| 4.25 | Simulated waveform of 6 $\mu$ A - 6 mA up transient w/ turbo                             | 78 |

|------|------------------------------------------------------------------------------------------|----|

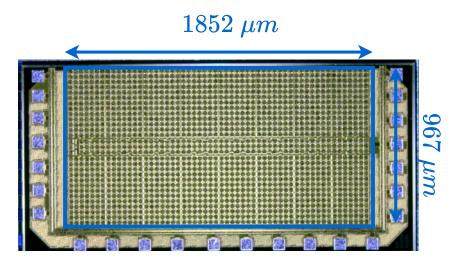

| 4.26 | Chip microphotograph.                                                                    | 78 |

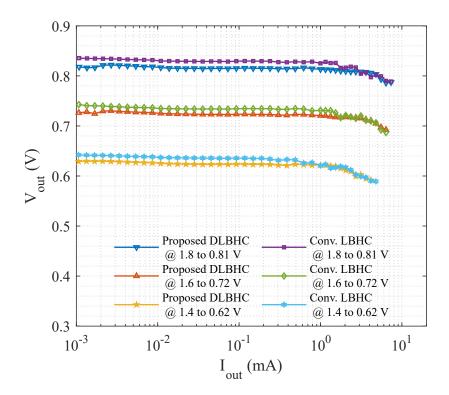

| 4.27 | Comparsion of the measured load regulation between the proposed                          |    |

|      | DLBHC and its conventional LBHC mode.                                                    | 79 |

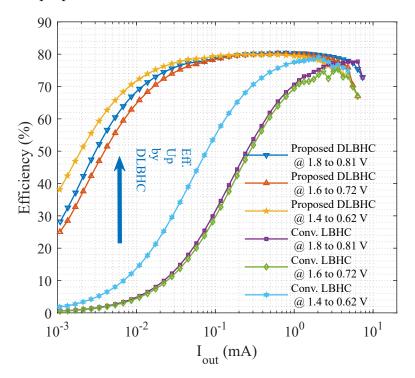

| 4.28 | Comparsion of the measured efficiency between the proposed DLBHC                         |    |

|      | and its conventional LBHC mode during load regulation                                    | 79 |

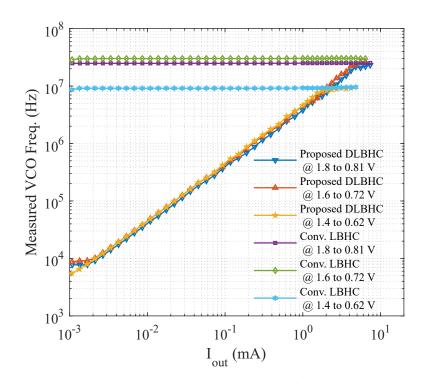

| 4.29 | Comparsion of the measured VCO frequency between the proposed                            |    |

|      | DLBHC and its conventional LBHC mode during load regulation                              | 80 |

| 4.30 | Comparsion of the measured line regulation between the proposed                          |    |

|      | DLBHC and its conventional LBHC mode                                                     | 80 |

| 4.31 | Comparsion of the measured efficiency between the proposed DLBHC                         |    |

|      | and its conventional LBHC mode during line regulation                                    | 81 |

| 4.32 | Comparsion of the measured VCO frequency between the proposed                            |    |

|      | DLBHC and its conventional LBHC mode during line regulation                              | 82 |

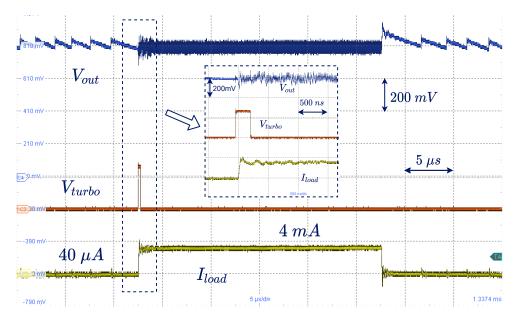

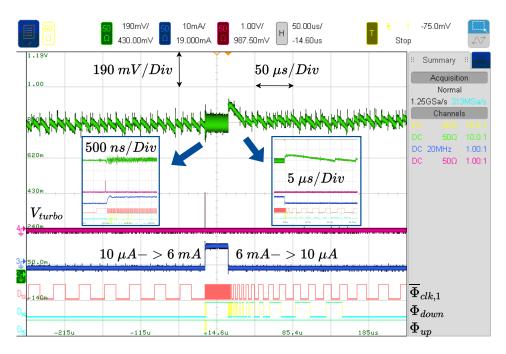

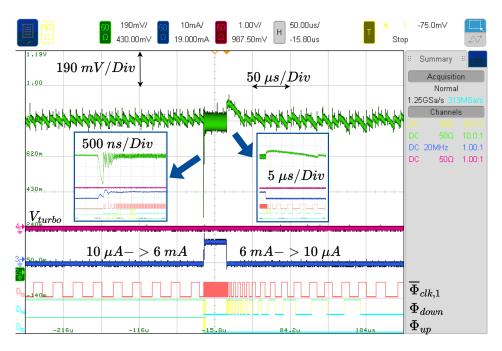

| 4.33 | Measured transient response w/ turbo from 40 $\mu$ A to 4 mA                             | 82 |

| 4.34 | Measured transient response w/ turbo from 10 $\mu$ A to 6 mA                             | 83 |

| 4.35 | Measured transient response w/o turbo from 10 $\mu$ A to 6 mA                            | 83 |

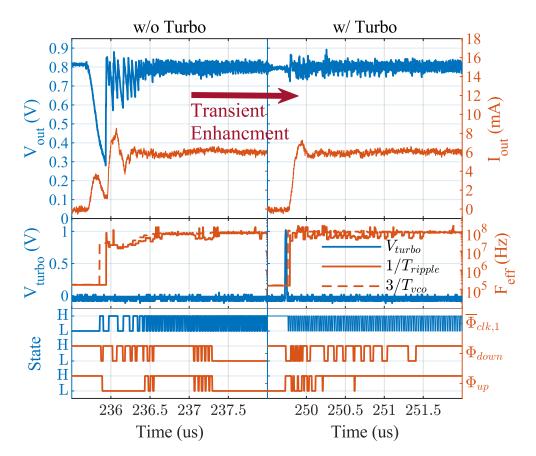

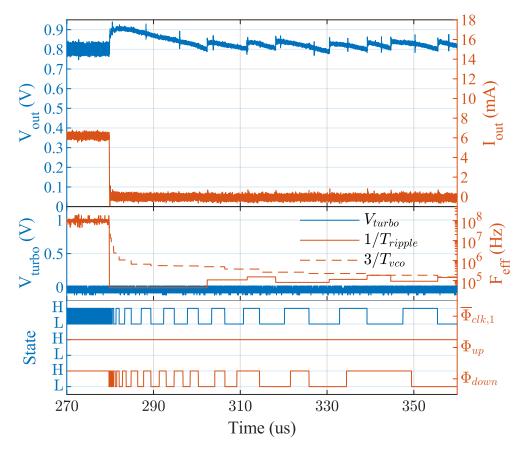

| 4.36 | Analysis and comparison between the measured step-up load tran-                          |    |

|      | sient w/o $V_{turbo}$ (left, from Fig. 4.34) and w/ $V_{turbo}$ (right, from Fig. 4.35). | 84 |

| 4.37 | Analysis of measured step-down load transient (from Fig. 4.34)                           | 85 |

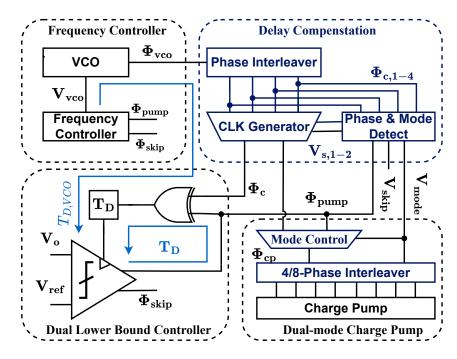

| 4.38 | Proposed centralized DLBHC controller with delay compensation                            | 87 |

| 4.39 | Analysis of DLBHC operations in time-domain: (a) Flowchart of op-                        |    |

|      | eration. (b) Steady-state with matched frequency. (c) Transient state.                   | 87 |

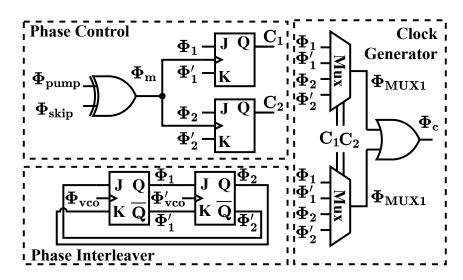

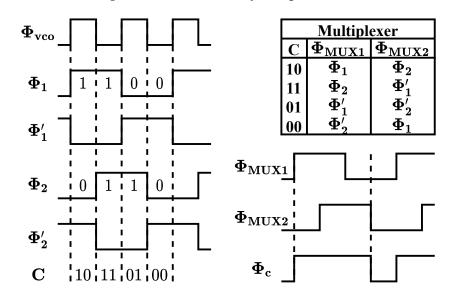

| 4.40 | Details of delay compensation.                                                           | 88 |

| 4.41 | Timing of delay compensation.                                                            | 88 |

| 4.42 | Simulated timing diagram of delay compensation during end of load                        |    |

|      | transient from 7 mA to 8 mA.                                                             | 89 |

| 4.43 | (a) Mode control circuit (b) Clock timing.                       | 89 |

|------|------------------------------------------------------------------|----|

| 4.44 | (a) State-detection (b) Frequency controller.                    | 90 |

| 4.45 | Chip microphotograph.                                            | 93 |

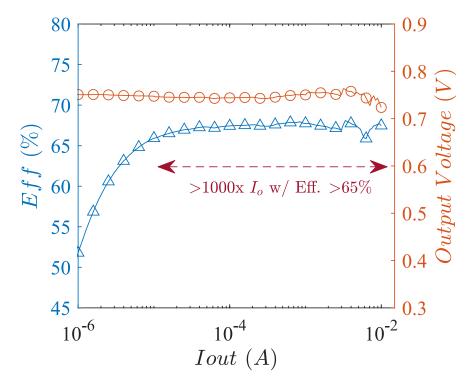

| 4.46 | Load regulation and efficiency.                                  | 93 |

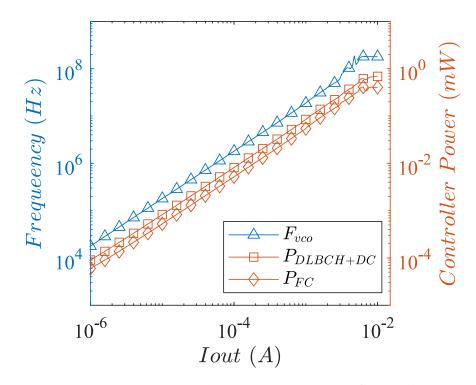

| 4.47 | Frequency and power consumption of controller                    | 94 |

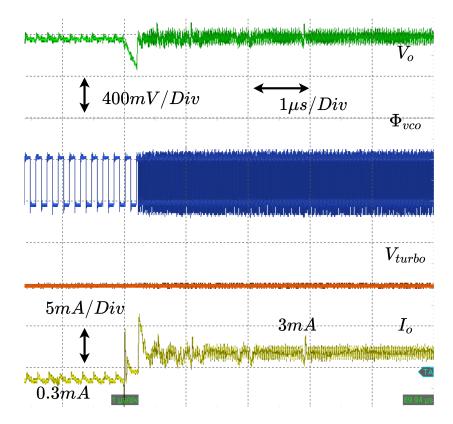

| 4.48 | Transient response without external activation.                  | 95 |

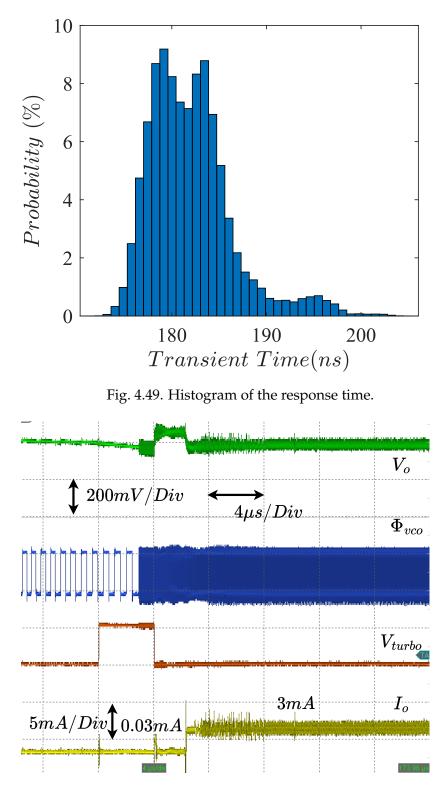

| 4.49 | Histogram of the response time                                   | 96 |

| 4.50 | Transient response with external activation.                     | 96 |

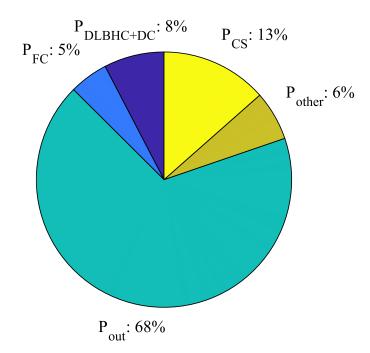

| 4.51 | Break down of power conversion efficiency at $1 mA$ load current | 97 |

# **List of Abbreviations**

| DLBHC | Dual Lower Bound Hysteresitc Control  |

|-------|---------------------------------------|

| DVFS  | Dynamic Voltage and Frequency Scaling |

| IoTs  | Internet-of-Things                    |

| LBHC  | Lower Bound Hysteresitc Control       |

| РСВ   | Printed Circuit Board                 |

| PMIC  | Power Management Integrated Circuit   |

| SCPC  | Switched Capacitor Power Converter    |

| SIPC  | Switched Inductor Power Converter     |

| VLSI  | Very Large Integrated Circuit         |

|       |                                       |

#### Chapter 1

### Introduction

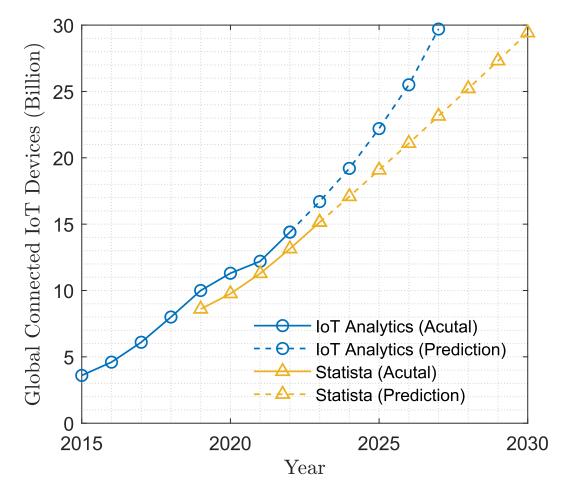

The Internet is connecting almost every electronic device in the world (Fig. 1.1): according to the statistics, the number of connected devices has increased from around 3.6 billion in 2015 to more than 15 billion in 2023 [1, 2]. Technological innovations in communication techniques, process nodes, sensor techniques and artificial intelligence (AI) have driven these increases over the past few years. These domains are expected to continue catalyzing IoT device development in the future. The rapid growth of IoT-connected devices presents challenges for circuit design. Many research efforts are dedicated to Very Large Integrated Circuit (VLSI) designs and systems-on-chip. These efforts aim to integrate multiple functions into a single chip and optimize power efficiency and performance to meet rising demand from applications. In this scenario, as the power source of every electronic device, the design and characteristics of Power Management Integrated Circuits (PMIC) have a direct influence on overall device effectiveness.

The process of DC-DC voltage conversion holds significant importance in system power conversion. Voltage regulation techniques have been developed to tackle the challenges presented in this area. These techniques include inductive DC-DC converters, capacitive DC-DC converters, low dropout regulators, and hybrid converters. In practical applications, it is common to see VLSI chips operating with varying supply voltages across different subsystems. Hence, there is a need for multiple

Fig. 1.1. Statistic and prediction of the number of connected devices from IoT Analytics [1] and Statista [2].

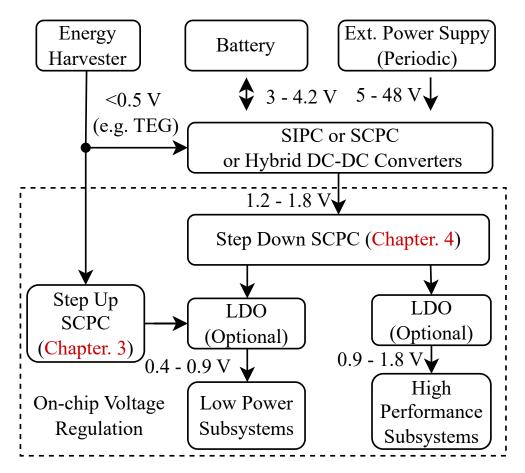

voltage regulators to facilitate voltage conversion across these domains. Considering Fig. 1.2 as an example, inductive or hybrid voltage regulators typically handle voltage conversion between the off-chip bus and load. Common scenarios include the charging of a battery using a Power Delivery (PD) charger that can manage voltages up to 48V [4–14], or delivering power from battery voltages to the chips [15–23]. This is feasible because the Switched Inductor Power converter (SIPC) can achieve high power conversion efficiency across a wide voltage conversion ratio. Generally, it offers high output power, making it suitable for powering the entire system.

Meanwhile, for on-chip voltage regulation, the Switched-Capacitor Power Converter (SCPC) as a type of PMIC is a competitive choice in many modern electronic

Fig. 1.2. Typical PMIC system in IoT devices.

devices. Compared to SIPC approaches, SCPC offers high-integrity design solutions using on-chip capacitors [24, 25]. In addition to compact design, SCPC can also achieve fast transient performance for load circuits. This makes it a promising choice for compact devices like Internet-of-Things sensors [26–35]. However, SCPC has intrinsic drawbacks in terms of voltage conversion ratio, efficiency, and output power. Therefore, this chapter provides a brief review of the pros and cons from three crucial aspects of PMIC: voltage conversion ratio, efficiency, and speed to establish the background for the following chapters.

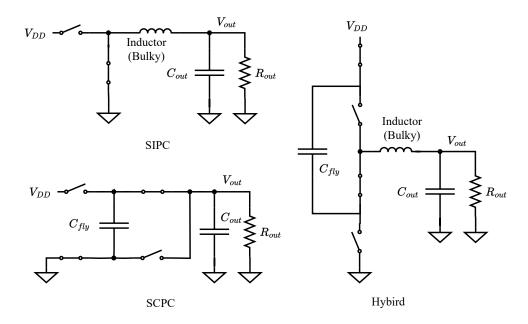

Unlike SIPC, which regulates the output voltage by controlling duty cycles with a single topology, SCPC has a fixed voltage conversion ratio for a given topology. Therefore, strategies for effectively covering the target design space have garnered

Fig. 1.3. Example of Step Down PMIC: SIPC, SCPC and Hybrid Converters.

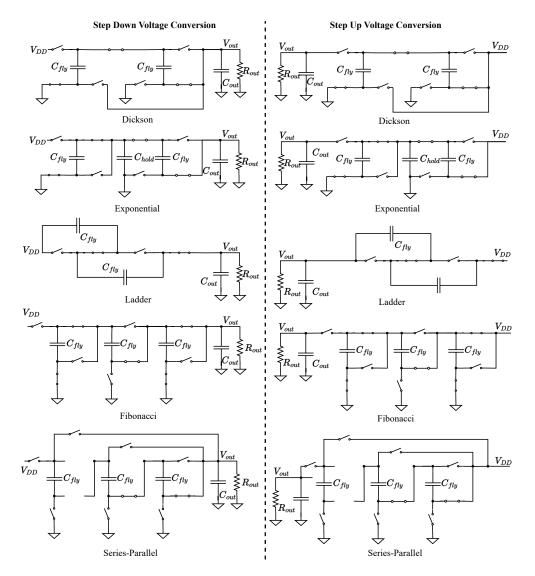

a great deal of research interest. Formulating a suitable topology appropriately to address the challenges of applications is one of the major research topics in this field. As shown in Fig. 1.4, basic SC topologies consist of Dickson, ladder, Fibonacci, series-parallel, and exponential converters. Exponential topologies provide the highest voltage conversion ratio but also magnify the parasitic losses from the bottom plate parasitic capacitance [36]. Dickson topology scales the conversion ratio linearly when stages increase, and the impact of the bottom plate parasitic is minimized with lower voltage swing [36]. However, for a high voltage conversion ratio, Dickson topology leads to more stages. Therefore, the overall losses induced by additional stages become non-negligible factors for this type of converter. Other topologies like Fibonacci or ladder structure take the trade-off between conversion ratio and parasitic losses, providing a more feasible choice for SC converter design. In addition to the basic topologies, techniques like multi-conversion ratio [37], successive approximation [38], and continuous ratio design are also being

Fig. 1.4. Typical SCPC converters comparison.

researched [39]. This endows SCPC with the potential to achieve competitive voltage regulation capability over other types of power converters.

In terms of efficiency, the Switched Inductor Power Converter (SIPC) is renowned for its high efficiency, primarily due to its high-quality, though often bulky, inductors. The inclusion of external inductors facilitates soft-charging during the transfer of charges across different levels. Unlike the SIPC, the Switched Capacitor Power Converter (SCPC), which lacks an inductor, has to mitigate hard-charge sharing losses to achieve competitive efficiency. As a result, within the scope of SCPC research, techniques such as split-phase [40] and multiphase soft-charging [41] have been developed to address this problem. It has also been reported that methods like scalable parasitic redistribution [42] can significantly reduce the impact of bottom plate parasitics by decreasing the voltage fluctuations across different phases. The integration of these techniques can lead to highly competitive efficiency levels in comparison to other types of converters.

When it comes to transient regulation, inductors tend to maintain a constant current. This intrinsic property allows SCPC converters to achieve faster regulation speeds compared to their SIPC counterparts. In fact, one method to enhance transient performance in a hybrid converter is having a capacitive path [43]. Within an SCPC, the controller regulates voltages by adaptively changing the switching frequency. To accomplish this, two of the most commonly used approaches are hysteretic control and frequency regulation. Hysteretic control involves comparing the output and reference voltages, triggering a phase switch when the output voltage falls below the reference voltage. When controlled by a hysteretic controller, an SCPC controller can respond within one clock cycle, demonstrating robust stability. However, a mismatch between optimum frequency and clock frequency may result in excessive subharmonic ripples [37, 42]. Frequency regulation, on the other hand, directly adjusts the operation frequency, thus avoiding the issue of subharmonic ripple. However, unlike hysteretic control, its response speed is limited by the controller's bandwidth. Consequently, achieving a fast transient speed with limited power becomes more challenging [44–46].

Given the advantages and challenges of SCPC, it is clear that a high-performance SCPC must incorporate techniques to improve efficiency and increase the number of available voltage conversion ratios in order to mitigate its drawbacks. This would allow it to combine the benefits of fast transient response speed and high power integrity, showcasing its superiority over SIPC in on-chip voltage regulation scenarios. Specifically, in applications such as always-on IoT sensors where power sources are limited, the critical issues of ultra-low-power/voltage optimization and standby efficiency/speed become prominent and also need to be addressed through thoughtful SCPC design.

In this thesis, two topics for further enhancing the SCPC performance will be discussed: In chapter 2, the challenges in always-on IoT sensor applications will be discussed in detail. In chapter 3, efficiency issues of the SCPC in the emerging thermoelectric energy harvesting applications will be addressed. Based on the critical trade-off between transistor performance and driving costs, our approach to optimizing gate voltage will be discussed and compared with other research to demonstrate why driving the transistor becomes one of the critical topics in energy harvesting applications. In chapter 4, a dual-loop hysteretic control-based frequency control method is discussed to enhance the transient performance of SCPC for Internet-of-Things (IoTs) applications, which minimizes the compromises required when trading off between speed and full-load range power conversion efficiency when implementing the controller. In chapter 5, the results obtained from these two pieces of research will be concluded, and the future development of SCPC will be discussed.

#### Chapter 2

### **Challenges in Always-On IoTs System**

Recently, there has been an increasing research interest in building always-on IoT terminals [47,48]. As shown in Fig. 2.1, a typical always-on IoT system usually consists of an ultra-low power process system and sensors for monitoring devices throughout the day, as well as a high-performance system to handle complicated tasks like processing and transferring data. In addition to the processing and sensor system, the PMIC needs to manage the voltage regulation for both the low-power and high-power modes of the system.

Because the energy sources of IoT devices are limited, extending the maintenance period of devices, or even eliminating the demand for replacing batteries, has garnered growing research interests in building energy harvesting circuits as the main or supplemental power sources in these IoT devices [26–35]. To achieve this goal, researchers are developing harvesters for different energy sources. The temperature gradient, which widely exists in the environment, is considered one of the promising energy sources for these devices. However, when thermoelectric materials are applied to IoT applications, new challenges arise. Despite the output power of a thermoelectric generator (TEG) varying with its materials and device dimensions, its closed-loop voltage is usually limited to hundreds of millivolts. Therefore, lowinput voltage DC-DC converters are necessary for thermoelectric energy harvesting in IoT applications.

Fig. 2.1. Challenges in Always-on IoT devices addressed by this thesis: energy harvesting (Chapter 3), standby efficiency and wake-up speed (Chapter 4).

When extending the discussion between SIPC and SCPC into the field of TEG energy harvesting: Inductive DC-DC converters usually have high efficiency, but bulky high-quality inductors are often required. This drawback is especially significant when it comes to lower power energy harvesting applications: a larger inductance is typically desired to decrease the operating frequency, thus achieving better power efficiency, even at lower levels.

However, while it is desirable to maintain high power conversion efficiency to maximize operational stability, integrity is also important in these cases. Two major benefits exist in fully integrated power converters for IoT applications. A fully integrated power converter not only reduces manufacturing costs by reducing components in PCB level design, but also contributes to the reduction of product sizes. Compact size is important for IoT sensors to minimize intrusion in people's daily lives. For example, in applications such as wearable sensors for Electrocardiography (ECG), a sensor with fewer inflexible components is critical for improving user comfort. Therefore, capacitive DC-DC converters, which can achieve fully integrated designs, are promising approaches for energy harvesting applications.

Compared with the photovoltaic energy harvest, thermoelectric generators have

Fig. 2.2. Review of PMIC performance: efficiency vs input voltage.

the benefit of being able to work with temperature differences even at night. However, small temperature differences pose the challenge of low output voltage in the power management domain. For example, a typical 2.5 cm x 2.5 cm thermoelectric generator has a closed-loop output voltage of less than 0.2V [73] when the temperature differences are below 7 degrees at the maximum power point and an output voltage below 8 mW [73]. The power scales with sensor size but the closed-loop voltage under the matching condition is less size-dependent, hence the power converter needs to address the low input energy harvesting problem. Fig. 2.2 reviews the power conversion efficiency of power converters under different input voltage conditions, and it can be observed that for SCPC, when the input voltage drops below 0.3 V reported by [61], existing approaches [26, 64] find significant difficulty in achieving high efficiency. The increased voltage ratio due to low input voltage, as

Fig. 2.3. Design Trade-offs in the controller design.

well as the insufficient gate, causes the degraded performance. The degradation of power conversion efficiency must be addressed to meet application requirements, and this thesis addresses the gate driving induced efficiency loss to boost the efficiency [59], which will be discussed in detail with Chapter 3.

In addition to searching for energy sources from the environment, the efficiency of utilizing the stored energy also plays an important role in operating the alwayson IoT devices. Most IoT devices spend a significant amount of time in low-power standby mode and are only activated for short periods as needed. Even if the power in standby mode is much lower than in active mode, the much longer standby time still pushes the total amount of consumed energy to a comparable level to the active mode. Therefore, the efficiency of both standby and active modes is critical for improving overall battery runtime. As a result, a high-efficiency converter over a wide range of loads is required. Additionally, fast transient speed is crucial for the responsiveness of IoT devices. As the load circuit must stand by until the PMIC output is ready to start its operations or until it can cope with a voltage drop during a transient event, a slow transition between the standby and active modes would significantly slow down the operation of the system. Unfortunately, just as high-performance cores require high power, a fast controller also requires more power. This leads to an inevitable trade-off between transient performance and light-load efficiency, as shown in Fig. 2.3. This limitation applies to almost all types of controllers but it can potentially be addressed at the system level. The always-on subsystem can notify the PMIC about potential wake-up events. Due to stability considerations of a control loop, not all control methodologies are capable of scaling their performance level internally and externally, hence, the dual lower bound hysteretic control is proposed in Chapter 4 to address this issue.

#### Chapter 3

# Efficiency Optimization in Low Voltage Low Power Applications

In previous research [27–32], different approaches are discussed to improve the efficiency of charge pumps in TEG energy harvesting applications. However, the efficiency and output power degradation is still significant when input voltage decreases. For example, reducing parasitic losses increases the peak efficiency [27, 28], but this approach cannot solve the problem of degraded on-resistance under low input voltage. Therefore, a significant drop in both efficiency and power appears. In addition to scaling the transistor, threshold modulation techniques like dynamic body biasing [29] also enhance the performance of transistors. However, external flying capacitors are still needed in [29], implying that this approach may not be effective in terms of improving the performance of the transistor to a level where fully integrated design is allowed. Another approach is to directly boost the gate voltage. Some researchers use bootstrapped ring-VCO (BTRO) to enlarge the amplitude of driving signals [32]. However, because the BTRO is not regulated, changes in input voltage can impact the frequency, and clock amplitude, and hence degrade the power conversion efficiency significantly. Moreover, in [30], a dual-mode 10-stage charge pump successfully improved the power density with an increased gate voltage. In [31], a gate-boosted charge pump design is also introduced with a significant improvement in output power. However, detailed analyses of the effects of increasing the gate driving voltage are still missing. As the voltage increases, scaling the switching transistors reduces the power required to drive it, but the parasitic losses on other parts of the controllers increase. This trade-off implies that detailed analysis may reveal the existence of an optimum point in charge pump design, which has the potential to become a competitive and cost-effective approach to improving performance.

#### 3.1 Trade-offs in SCPC Design

#### 3.1.1 Conduction Losses

In a regulated SCPC converter, the transistor on-resistance determines the lowest conduction losses that can be achieved, and the conduction losses are a direct result of hard-charge sharing losses under slow switching limits (SSL).

Consider a circuit with two capacitors and a resistor, which holds an initial capacitor voltage  $V_{C1} + \Delta V$  and  $V_{C1}$ . Assuming that a  $\Delta V$  voltage change occurs during one phase, compare the initial state energy:

$$E_{init} = \frac{1}{2}C((V_C + \Delta V)^2 + V_C^2)$$

(3.1)

the final state has an energy of

$$E_{end} = \frac{1}{2}C((V_C + \frac{1}{2}\Delta V)^2 + (V_C + \frac{1}{2}\Delta V)^2)$$

(3.2)

the overall energy stored in the circuit is reduced by:

$$\Delta E_{loss} = \frac{1}{2}C(\frac{1}{2}\Delta V^2) \tag{3.3}$$

This is usually referred to as hard-charge sharing losses. Meanwhile, the energy transferred to  $C_2$  is:

$$\Delta E_{C2} = \frac{1}{2}C(V_C\Delta V + \frac{1}{4}\Delta V^2) \tag{3.4}$$

Because the conduction losses scale quadratically with the voltage changes  $\Delta V$ , while the transferred energy scales linearly with the  $\Delta V$ , it motivates techniques like split-phase [40] and multiphase soft-charging [41] to minimize the  $\Delta_V$  across each stage to enhance the power conversion efficiency.

Regarding the impact of conduction losses in regulated SCPC, because the conduction losses are proportional to  $\Delta V^2$ , the overall conduction losses in SCPC are proportional to the deviation of the output voltage from the topology's ideal voltage conversion ratio,  $\Delta V_{out}$ . This result is trivial as  $\Delta V_{out}$  is accumulated from the voltage drop at each stage. Therefore, conduction losses are usually considered constant in regulated SCPC. However, this doesn't mean that conduction losses are irrelevant to the circuit design. In fact, the minimum achievable conduction losses are closely related to the circuit and are usually discussed alongside the Slow Switching Limit (SSL) and Fast Switching Limit (FSL) in the literature.

#### 3.1.2 Impact of Slow and Fast Switching Limit in Conduction Loss

In practice, because the overall conduction losses are proportional to  $\Delta V_{out}^2$ , it is desired to minimize the voltage drop over the whole operating range. One of the necessary conditions to guarantee that voltage drop can be minimized is that the SCPC needs to have its charge transferred almost completely. This usually refers to the Slow Switching Limit (SSL) of SCPC, where the voltage drop across the switches and interconnect are small enough to be considered almost ideal.

To ensure this condition applies, according to the principle of RC charging and discharging, the time constant needs to be short enough compared to the period of

each phase. If the time constant is comparable to the period of each phase, then the SCPC will enter the Fast Switching Limit (FSL). As the voltage drop across each stage cannot be ignored, it causes additional voltage drops and consumes the voltage headroom of the SCPC: Taking the circuit in chapter 3.1.2 as an example, due to the existence of voltage drop over resistors *R*, the  $\Delta V$  that can be transferred is reduced by  $I_{RC}R$ . This reduces the transferred charge by  $\Delta Q = I_{RC}RC$ . In a regulated SCPC, the degraded charge transfer capabilities need to be compensated for by increasing the operating frequency for a fixed load current. But on the other hand, the increased frequency will push the SCPC closer to the FSL limit. Hence, while the SCPC usually scales the frequency linearly with load current, the relationship is no longer linear, and the frequency is increased rapidly when the operating region is close to FSL. Moreover, if all the voltage headroom is consumed by the resistance's voltage drop, the SCPC will fail to reach the designed output voltage.

In fact, these characteristics are predictable from the behavior of the RC charging and discharging curve. By defining a time constant *RC*, an initial current  $I_{init}$ , and a final voltage change  $\Delta V_{end}$ , at 2*RC*, the voltage change is about 86% $\Delta V_{end}$ , and at 3*RC*, it reaches 98% $\Delta V_{end}$ . While the current flow, as well as the voltage drop across the resistor, reduces to 14% $\Delta V$  and 5% $\Delta V$  respectively. Hence, although the transition between FSL and SSL is not clearly defined, it is roughly at the level of the time constant. Overall, a regulated SCPC operates in SSL for most of its operating ranges, and the transition point to FSL determines the maximum achievable load current level. Therefore, given a target level of conduction losses ( $\Delta V_{out}$ ), the maximum load current level is determined by the FSL limit and hence by the quality of the switches and interconnect (*R*). In other words, given a target load current level, the minimum conduction loss level is determined by headroom to FSL limit at current operating conditions.

Overall, the higher the switches and interconnect quality (which suggests a lower

$R_{on}$ ), the higher the achievable performance. In fact, for detailed topology, the impedance model, which models the SCPC with an ideal transformer and resistor, provides a powerful approach to quantitatively analyze the issue. A smaller impedance in general would lead to lower conduction losses and higher efficiency. But in this thesis, the qualitative impact of  $R_{on}$  on SCPC is sufficient for the subsequent discussions, hence a detailed review is omitted here.

#### 3.1.3 Switching Losses

While the conduction loss is proportional to the voltage drop from the ideal output voltage  $\Delta V_{out}$  and can be considered constant when the output voltage is regulated by the controller, several other types of switching losses exist in the SCPC that will affect its overall power efficiency.

Bottom-plated parasitic capacitance is one of the representative capacitive switching losses in SCPC. In on-chip capacitors, while the capacitance between the top and bottom plate is of interest to the circuit designer, both the top and bottom plates come with parasitic capacitance relative to ground nodes (or could be other circuit nodes depending on layout). The parasitic capacitance can significantly vary with the type of capacitor. Metal-insulator-metal (MIM) capacitor is one of the most commonly used on-chip capacitor types in modern CMOS technologies. As the MIM capacitors are usually located at higher metal layers and are placed vertically, they come with smaller bottom plate parasitic capacitances to the bulk silicon and negligible top plate parasitic capacitors are fabricated in lower layers of the chips, in which capacitors are much higher than in the MIM capacitors. Using metal fingers also implies that the capacitance density of MOM capacitors heavily depends on the process nodes: a process with more metal usually allows higher-density MOM capacitors.

In practice, while on-chip capacitors usually can achieve higher power density compared with their off-chip counterparts, the limited area still puts significant limits on the overall capacitance available on-chip. Therefore, to maximize the capacitance available on chips, the MIM capacitors and MOM capacitors can be stacked together to further increase the capacitor density, but at the cost of increasing the bottom plate parasitic capacitance of the MIM capacitor. Additionally, techniques like scalable parasitic redistribution [42] are developed to reduce the impact of parasitic capacitance. Overall, the bottom plate parasitic capacitance-induced power losses are topology and process dependent.

Gate capacitive losses are also one of the representative power losses in the SCPC. In fully integrated SCPC, the gate parasitic is scaled with transistor sizes and can be approximated by:

$$C_{gate} \approx C_{ox}WL + C_{ov}W \tag{3.5}$$

where  $C_{ox}$  is the oxide capacitance between the gate and channel, and  $C_{ov}$  is the capacitance that exists between the gate and drain/source, which is dominated by the width of transistors. Because power transistors in SCPC usually take a minimal length, the gate parasitic capacitance scales linearly with the transistor width. Hence the power consumption of the gate scales linearly with the transistor width and quadratically with the gate driving voltage. Scaling the gate driving voltage and transistor width also changes the on-resistance  $R_{on}$  of switches, hence leading to a trade-off between the current and efficiency.

Other types of switching losses also include the reverse leakage current when SCPC changes the phases, but these losses are highly design specific and can be avoided by techniques like deadtime design. Also, for both the gate and parasitic capacitance induced losses, because the parasitic RC loop holds a smaller time constant due to its small parasitic capacitance, the charge transferred per phase is considered complete. Therefore, with a fixed flying node voltage and gate driving voltage in regulated SCPC, the parasitic losses mainly scale with the operating frequency.

#### 3.1.4 Trade-offs in Low Voltage Low Power Applications

Due to the existence of conduction losses and switching losses, there is a tradeoff between the maximum output current and efficiency. As it is summarized in Fig. 3.1, for charge pumps with ideal switches, because the effective internal resistance generates voltage drop  $V_{drop}$  from ideal voltage conversion ratio  $(N + 1)V_{DD}$ and leads to conduction losses [27], the charge pump efficiency is limited by the trade-off between output current  $I_{out}$  and  $V_{drop}$ . However, when maximizing  $I_{out}$ and minimizing  $P_c$ , the best achievable result is limited by the maximum frequency that can be achieved. Such a frequency limitation f is generated by the on-resistance  $R_{on}$  of switches. If the switching frequency is too high, the flying capacitors cannot be effectively charged or discharged, generating additional resistive losses on transistors and hence degrade the overall efficiency.

A reduced input voltage and power further amplify the impacts of these tradeoffs: while the reduced voltage increases the impact of conduction losses for the same voltage drop, the switching power required for reducing the on-resistance hence maintaining a small voltage drop also cannot be ignored. Therefore, it is not difficult to realize that the on-resistance of transistors is a critical parameter when the input voltage is reduced, and the effectiveness of the methods for reducing  $R_{on}$ determines the final performance. As mentioned in the introduction, methods like body-biasing, transistor scaling, and gate voltage can effectively reduce the  $R_{on}$ .

Fig. 3.1. Charge pump design trade-offs.

However, the effectiveness is different for these methods and can be investigated by comparing the required power of controller  $P_{control}$ . If transistor scaling is the only method applied to transistors, it is difficult to compensate for the exponential relationship between currents and voltage in the subthreshold region, hence resulting in a significant  $P_{control}$  and degrading the efficiency. Meanwhile, because  $V_{th}$  is a weaker function of body-biasing voltage  $V_b$  than  $V_{gs}$ , adjusting body-biasing is less effective than directly changing the  $V_{gs}$ . Therefore, optimizing  $V_{gs}$ , which reduces  $R_{on}$  with minimized increment in  $P_{control}$ , is a promising approach for designers to maximize their charger efficiency. The concept of gate voltage optimization is proposed.

# **3.2** Gate Voltage Optimization for Target *R*<sub>on</sub>

### 3.2.1 Gate Voltage Optimization in Strong Inversion Region

Because the output voltage is specified by applications and regulated by feedback loops, an SCPC usually has fixed conduction losses  $P_c$ . Generally, chargesharing losses, which are the losses generated during the charge redistribution process, are the main source of conduction losses. From this viewpoint, for any given load, because the total loss can be written as:

$$P_{loss} = P_s + P_c = P_{s,sw} + P_{s,c} + P_{s,etc} + P_c$$

(3.6)

With a fixed  $P_c$ , the target would hence be to minimize switching losses  $P_s$ . Part of  $P_s$ , such as the bottom plate parasitic capacitance-induced losses, is related to the charge pump operating voltages of each stage. Similar to conduction loss, it can be considered a constant because our method does not change the operation voltage of each stage during optimization. These  $V_{gs}$  independent losses hence are summarized as  $P_{s,etc}$ . Meanwhile, gate parasitic capacitance of switch transistors  $P_{s,sw}$ , which is expected to be scaled with  $V_{gs}$ , can be written as:

$$P_{s,sw} = C_{sw} V_{gate}^2 f = C_{ox} W_{sw} L_{sw} V_{gate}^2 f$$

(3.7)

$C_{sw}$  is the gate parasitic capacitance of each transistor, which can be further expressed by parasitic capacitance per unit area  $C_{ox}$ , transistor width  $W_{sw}$  and length  $L_{sw}$ .  $V_{gate}$  is the voltage applied to the gate of transistors. Meanwhile, although the power consumption of the controller varies with different designs, capacitive switching losses of the controller  $P_{s,c}$  is selected to model the general behavior of

control and derive the general considerations of charge pump designs:

$$P_{s,c} = C_c V_{gate}^2 f \tag{3.8}$$

where  $C_c$  is the effective controller parasitic capacitance to each switching transistor.

When scaling the  $V_{gs}$  and transistor sizes, a scaling rule must be defined to maintain a constant charge pump RC-loop characteristic. This implies that key parameters, such as the charge pump frequency of the regulated charge pump, do not need to be changed during the optimization. To achieve this, the *R*<sub>on</sub> of the charge pump is selected as the unchanged parameter during the scaling process. While charge pump optimization is a multidimensional problem, encapsulating the charge pump performance with a single parameter aids us in discussing the optimization problem in an extra dimension of controller and gate driving losses. Hence, discussing the optimum point within the optimization space becomes more convenient. To introduce our proposed method, let us first assume that  $R_{on}$  is the optimum choice for the charge pump, for the sake of simplicity. It's important to note that this is essential in guaranteeing that the resulting  $P_s$  is minimal. The following analysis will provide verification of whether this assumption is reasonable. For conceptual analysis, assuming the voltage is sufficient for transistors to operate in the triode region. In the triode region, the relationship between gate to source voltage  $V_{gs}$  and transistor width  $W_{sw}$  can be derived as:

$$W_{sw} = \frac{L_{sw}}{\mu R_{on} C_{ox} (V_{gs} - V_{th} - V_{ds}/2)}$$

(3.9)

Replacing the  $W_{sw}$  in (3.7) hence leads to:

$$P_{s,sw} = \frac{L_{sw}^2 V_{gate}^2 f}{\mu R_{on} (V_{gs} - V_{th} - V_{ds}/2)}$$

(3.10)

For simplicity, a PMOS connected to the output node is chosen to demonstrate the concept. Other transistors can be discussed by modifying the  $V_{gate}$  and  $V_{gs}$ . In this case, output is the highest voltage available in the system. The  $V_{gs}$  hence equals to  $V_{gate}$ . Therefore, the overall power consumption in the triode region can be written as:

$$P_{s} = V_{gs}^{2} f\left(\frac{L_{sw}^{2}}{\mu R_{sw,on}(V_{gs} - V_{th} - V_{ds}/2)} + C_{c}\right)$$

(3.11)

Observing (3.11), it is not difficult to notice that both the f and  $R_{sw,on}$  appear. If other parameters of the charge pump are already given, then each  $R_{sw,on}$  would correspond to a different f. Since the proposed scaling does not alter the  $R_{sw,on}$ , both  $R_{sw,on}$  and f can be considered as constants. Therefore, it is not difficult to compare the result obtained with different  $R_{sw,on}$  and determine the optimum  $R_{sw,on}$ . Assuming that  $R_{on}$  is the optimum choice of the charge pump at the beginning of the analysis is hence a reasonable choice.

By taking the partial derivative of (3.11), the total switching losses can hence be reduced, if:

$$\frac{\partial P_s}{\partial V_{gs}} = V_{gs} f[2(C_{sw} + C_c) - \frac{C_{sw} V_{gs}}{V_{gs} - V_{th} - V_{ds}/2}] < 0$$

(3.12)

To simplify the expression, define  $C_c = kC_{sw}$ . We observe that (3.12) is negative, if:

$$V_{gs} < 1 + \frac{1}{2k+1} \tag{3.13}$$

Therefore, an upper limit of  $V_{gs}$  is given by (3.13).

The concept  $V_{gs}$  optimization can thus be summarized as shown in Fig. 3.2. At high  $V_{gs}$ , the losses on the switches become less sensitive to changes in their gate driving voltage, and the controller losses  $P_{s,c}$  would gradually dominate over the overall system losses. Conversely, at a lower voltage, the losses on the switches become more sensitive to changes in their gate driving voltage, and the overall losses

Fig. 3.2. Conceptual graph of optimum gate voltage.

would gradually be dominated by the  $P_{s,sw}$ . An optimum point thus exists.

In practice, the assumptions in (3.13) have limitations. For example, the theory of transistor scaling based on (3.9) becomes less convincing when the transistor operates around the transition region of weak and strong inversion. However, because the degradation of the transistor's conductivity occurs much faster in weak inversion regions, this would result in similar behavior as described in Fig. 3.2. The prediction made by (3.13), therefore, remains meaningful to the circuit designers. It allows them to utilize the conclusion to estimate the benefits of optimizing  $V_{gs}$  in their respective applications.

### 3.2.2 Gate Voltage Optimization in Weak Inversion Region

To build a better understanding of gate voltage optimization, this section introduces an enhanced model to address the limitations presented in section 3.2.1 and aligns with the simulation results. To achieve this, effective gate-to-source voltage  $V_{gsteff}$  and effective channel length  $L_{eff}$  need to be introduced.

In the BSIM3 model [74], the drain-source current of different regions can be defined as:

$$I_{ds} = I_{dso} F(V_{ds}, V_{gs})$$

(3.14)

where  $F_{Vds,Vgs}$  summarizes non-dominated effects such as drain-induced barrier lowering, substrate current body effect, velocity saturation, and parasitic drainsource resistances. The  $I_{dso}$  can be written as:

$$I_{dso} = \mu_{eff} \frac{W_{eff}}{L_{eff}} C_{ox} V_{gsteff} (1 - \frac{A_{bulk} V_{dseff}}{2(V_{gsteff} + 2v_t)}) V_{dseff}$$

(3.15)

where effective width  $W_{eff}$ , length  $L_{eff}$ , mobility  $\mu_{eff}$ , gate-to-source voltage  $V_{gsteff}$ , and drain-to-source voltage  $V_{dseff}$  are introduced to better represent transistor physics. Among these parameters,  $W_{eff}$  is very close to the actual transistor geometry because the transistor is large in the weak inversion region. The small voltage between terminals also does not generate significant impacts on effective mobility  $\mu_{eff}$ . However, the effective channel length  $L_{eff}$  and gate-to-source voltage  $V_{gsteff}$  have important impacts on the results.

For the 180-nm CMOS process, the differences between the effective channel length  $L_{eff}$  and the actual transistor geometry cannot be ignored. Actually,  $L_{eff}$  is smaller than the actual transistor size, leading to higher current and smaller power losses in the simulation results.

$$V_{gsteff} = \frac{2nv_t ln[1 + exp(\frac{V_{gs} - V_{th}}{2nv_t})]}{1 + 2nC_{ox}\sqrt{\frac{2\Phi_s}{q\epsilon_{si}N_{ch}}}exp(\frac{-V_{gs} - V_{th} - 2V_{off}}{2nv_t})}$$

(3.16)

Detailed definitions of the parameters in (3.16) can be found in the BSIM3 manuals [74], and most parameters can be directly extracted or calculated from the PDK. The

Fig. 3.3. Circuit setup for evaluating the transistor scaling under different  $V_{gs}$ .

power losses on the transistor hence are modified as:

$$P_{s,sw} = \frac{L_{sw}L_{sw,eff}V_{gate}^{2}f}{\mu R_{on}(V_{gsteff} - \frac{V_{ds}}{2(V_{gsteff} + 2v_{t})})}$$

(3.17)

Generally, the  $V_{gsteff}$  is larger than the  $V_{gs} - V_{th}$  when  $V_{gs}$  is close to or smaller than the threshold voltage. As a result, smaller transistor sizes and power losses are expected in simulations.

#### 3.2.3 Numerical Calculation

As previously mentioned, constant performance is necessary when scaling the transistors and optimizing the gate voltage for the charge pump. The setup of the experiment can be seen in Fig. 3.3. In this simulation, we define T = 3RC as the point where the two circuits are compared. The simulation includes the impact of changes in source voltage. For a 5-stage charge pump with 120 mV input voltage and 600 mV output voltage, the average voltage drop across each switching transistor is around 20 mV. Therefore, the initial capacitor voltage is set to 100 mV, and  $V_{DD}$  is set to 120 mV. Since the NMOS transistor source is shifted by a  $V_{DD}$ , (3.11) needs modification as follows:

$$P_{s} = V_{gate}^{2} f\left(\frac{L_{sw}^{2}}{\mu R_{sw,on}(V_{gs} - V_{th} - V_{ds})} + C_{c}\right)$$

(3.18)

Fig. 3.4. Extraction of the  $V_{th}$  from simulation results.

where  $V_{gate}$  can be expressed as  $V_{gs} + V_{ds}$ . To account for source voltage changes,  $V_{ds}$  is set to half of the voltage drop, which equates to 10 mV in this calculation. This approximation sacrifices some accuracy to maintain simplicity. While process-related parameters can be obtained from the PDK,  $V_{th}$  must be extracted using the  $I_{ds}/\sqrt{g_m}$  method [75] for optimal fitting. Fig. 3.4 demonstrates that the typical  $V_{th}$  is 540 mV.

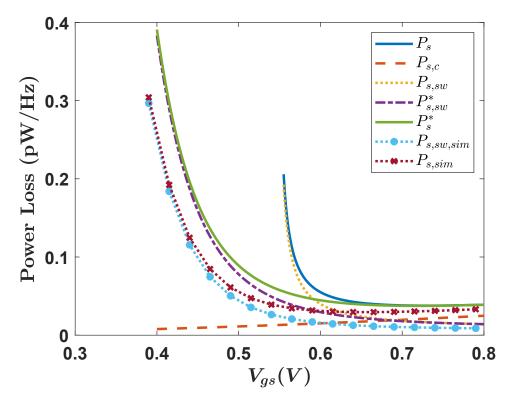

Fig. 3.5 and Fig. 3.6 show the result of a normal threshold NMOS transistor with 180 nm channel length. If designed minimal charge/discharge time is 3RC, the time constant needs to be smaller than 1/6f. Taking 1 MHz as the target frequency and 50 pF as the pumping capacitor, the on-resistance needs to be smaller than 3.3 k $\Omega$ . Hence, 3 k $\Omega$  on-resistance is taken for calculation and simulation in Fig. 3.5. At higher power, a 200  $\Omega$  on-resistance is taken in Fig. 3.6 for comparsion. The simulated power loss on transistor switches is plotted as the *P*<sub>s,sw,sim</sub>, the result calculated

Fig. 3.5. Verification of the theory when  $R_{on} = 3000\Omega$ .

from (3.10) is plotted as  $P_{s,sw}$  and the result calculated from (3.17) is plotted as  $P_{s,sw}^*$ . Because the overall optimum point is achieved by trading-off the  $P_{s,sw}$  and  $P_{s,c}$ , The  $P_{s,c}$  needs to be modeled to calculate the optimum point. The  $P_{s,c}$  is the power losses on the controller which does not drive the switches directly. Usually,  $P_{s,c}$  heavily depends on the controller design. In this analysis, the power losses generated by parasitic capacitance are considered. Typically, the metal line capacitance ranges from 0.01 to 0.2 fF/um. It is hence reasonable to assume  $C_c$  is 30 fF for analysis, and the corresponding controller losses can be plotted as  $P_{s,c}$  in Fig. 3.5 and Fig. 3.6. By adding up the  $P_{s,c}$ , the overall switching loss can be plotted as  $P_s$ ,  $P_s^*$ , and  $P_{s,sim}$ , where  $P_s$  is the result of (3.18),  $P_s^*$  is the result based on (3.17), and  $P_{s,sim}$  is the result of simulation.

Fig. 3.5 and Fig. 3.6 provide a basis for discussing the accuracy and implications

Fig. 3.6. Verification of the theory when  $R_{on} = 200\Omega$ .

of previous analyses. When identifying the optimal gate voltage, the method presented in section 3.2.1 can yield accurate results, provided the switches operate in the triode region. However, because (3.18) does not include the weak inversion region, errors are introduced when  $V_{gs}$  is close to  $V_{th}$ . Despite the uncertainties that arise during the early stages of circuit design, the simple estimation offered by (3.18) proves useful, as it indicates the approximate range for the optimal gate voltage. For a more precise analysis, designers should use (3.17) to optimize performance effectively.

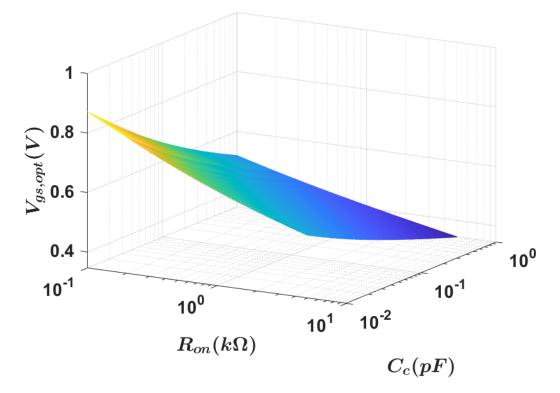

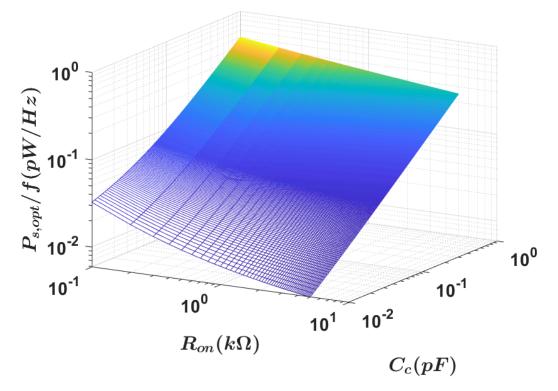

Furthermore, the optimal gate voltage largely depends on the controller and  $R_{on}$ . To discuss the wide-ranging impact of  $P_{s,c}$  at various output power levels, the optimal gate voltage and minimum power losses are computed based on (3.17). Fig. 3.7 shows the result of optimum gate voltage. Unless a small  $C_c$  and  $R_{on}$  can be achieved simultaneously, which is difficult in thermoelectric energy harvesting, the optimum

Fig. 3.7. Optimum gate voltage at different  $R_{on}$  and  $C_c$ .

gate voltage is more likely to be located at a lower voltage. Meanwhile, as it is shown in Fig. 3.8, a high  $C_c$  and  $R_{on}$  is usually undesired due to its large power losses, the resulting optimum gate voltage hence generally locates near the threshold voltage. Moreover, although the optimum  $V_{gs}$  can be changed at different load current levels, which is equivalent to optimize the circuit for the corresponding optimum  $R_{on}$ , the results of Fig. 3.7 and Fig. 3.8 shows that the difference between these optimum points is less significant. Optimizing the  $V_{gs}$  for maximum load current condition hence can be considered sufficient in most cases.

It's also worth mentioning that the power, being specific to controller design, may not always align with the ideal capacitive loss model. In general,  $P_{s,c}$  will increase with  $V_{gs}$  for most controllers, although the slope can differ. For instance, when level shifters are introduced, while most parts of the controller are supplied with a constant voltage, the level shifter still consumes extra power for larger  $V_{gs}$ .

Fig. 3.8. Power losses at optimum gate voltage with different  $R_{on}$  and  $C_c$ .

As the optimal  $V_{gs}$  results from the trade-off between controller power and switch power,  $V_{gs}$  would place at a higher value if  $P_{s,c}$  is lower and the change rate versus  $V_{gs}$  is slower. Also, as the reduction of  $P_{s,sw}$  at higher  $V_{gs}$  is less significant and  $P_{s,sw}$ might be insignificant compared to output power, the actual benefits of these approaches need to be assessed on a case-by-case basis. Overall, the analysis process is like the previous one, except  $P_{s,c}$  needs to be replaced with the actual model.

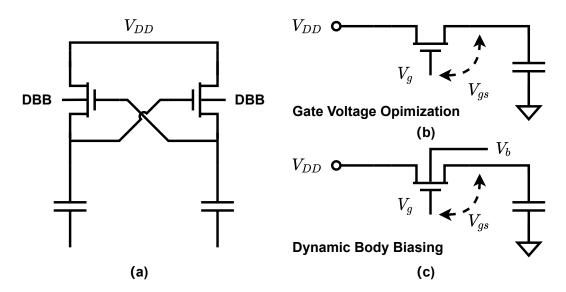

### 3.2.4 Comparison with Dynamic Body Biasing

In terms of improving the performance of charge pumps for energy harvesting applications, a competitive approach is dynamic body biasing. For example, dynamic body biasing (DBB) is introduced in [29] to enhance charge pump performance. In their research, forward body bias is applied to an NMOS transistor when

Fig. 3.9. (a) Circuit setup of typical charge pumps with DBB. (b) Setup of gate voltage optimization for simulations. (c) Setup of DBB for simulations.

charging the flying capacitors. Reverse bias is applied to the NMOS transistors dynamically when discharging the flying capacitors. The threshold voltage hence is dynamically modified for a better performance.

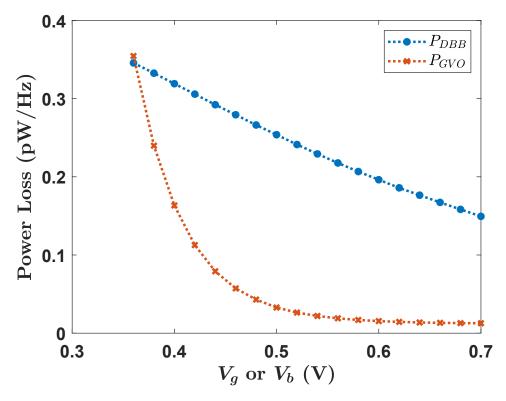

To compare the performance differences between gate voltage optimization and body biasing techniques, this paper simulates and analyzes the impacts of applying these techniques. Fig. 3.10 shows the concept of DBB described in [29] and the simulation setup for this comparison. The target equivalent on-resistance is 200 ohms. For gate voltage optimization, the body of NMOS transistors is connected to the ground. The transistor width is scaled at different  $V_g$  to maintain constant performance. In DBB-based circuits, cross-coupled designs make the effective  $V_{gs}$  close to  $V_{DD}$ . Therefore,  $V_g$  is set to  $2V_{DD}$  when the transistor is turned on, and  $V_{DD}$  when the transistor is turned off. To maintain a constant performance, the transistor is scaled with different forward biasing voltage  $V_b$  and is biased to the ground before the transistor is turned on. Therefore, the power consumption of switching bodybiasing voltage also needs to be considered. Taking  $V_{DD} = 120mV$ , the result can be plotted as Fig. 3.10. Both transistors are low-threshold transistors. The horizontal

Fig. 3.10. Comparison between dynamic body biasing and gate voltage optimization.

axis is  $V_g$  for gate voltage optimization and  $V_b$  for DBB.

The graph illustrates that the overall power consumption of DBB is higher than that of the proposed approach at high biasing voltages, suggesting that gate voltage optimization is more effective than body biasing. This is aligned with common sense because of the weak relationship between threshold voltage and body biasing. Because gate voltage optimization usually can be achieved by careful design of the controller without modifying its structure significantly. The proposed method hence is a more cost-effective approach to improve the overall power conversion efficiency.

Fig. 3.11. The general consideration of determining the optimum gate voltage.

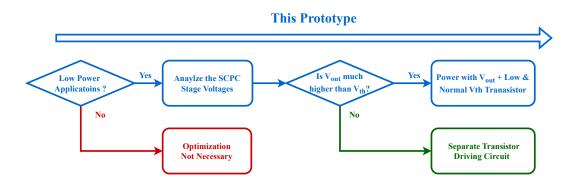

#### 3.2.5 Summary of Methodology

Overall, we can summarize a practical design flow as depicted in Fig. 3.11. Initially, it is desirable to determine whether the power level of the target applications could make the cost of implementing the controller a dominant factor. If so, optimizing the gate voltage becomes necessary for enhancing power conversion efficiency. Generally, power losses on the switches decrease when the  $V_{gs}$  increases. However, in energy harvesting application, this effect becomes less influential compared to capacitive loss at high  $V_{gs}$ . Consequently, the impact of capacitive loss on the  $P_{s,c}$ gradually dominates the overall losses in the proposed model. Meanwhile, a small  $R_{on}$  usually indicates that the power converter is designed for high-power applications, causing  $P_{s,sw}$  to increase and dominate the overall losses even at higher  $V_{gs}$ levels.

In terms of determining a practical  $V_{gs}$ , non-ideal effects must also be taken into account. For instance, leakage current also scales with  $V_{gs}$ , shifting the optimum  $V_{gs}$  to a lower value. Despite this, in the subthreshold region, the benefits gained from increased speed with higher voltage typically outweigh its cost. Therefore, designing the gate-to-sources voltage of switches around the threshold voltage in energy harvesting applications usually results in performance levels close to the optimum of each stage. Likewise, designing a controller near the threshold voltage promotes a balanced trade-off between performance and power.

Thus, the designer should verify if the target output voltage is proximate to the threshold voltage, which is often the case when supplying power to lower power circuits. A combination of different  $V_{th}$  options and full voltage driving from output is usually sufficient for achieving excellent performance since the cost of the controller can be minimized with its simplified design. If this condition does not apply, separate gate driving circuits might be necessary, requiring case-by-case discussion. For example, some middle stages could be used to supply the voltage levels, thus minimizing the number of level shifters and their powers. Overall, balancing the transistor and the controller becomes critical in optimizing gate usage for energy harvesting SCPC.

#### **Implementation and Verficiation** 3.3

#### 3.3.1 Verficiation Circuits

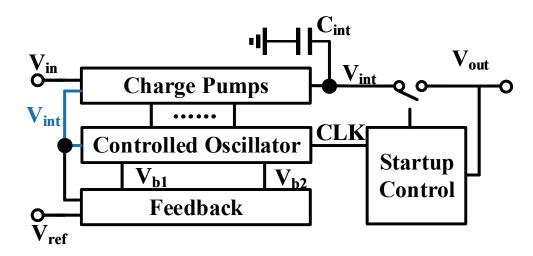

Based on the above general discussion about  $V_{gs}$  optimization for a single stage of the charge pump, we will discuss our design considerations in this section. The aim is to illustrate the practical application of the general conclusions from Section II to the design process of charge pumps for energy harvesting applications. Fig. 3.12 depicts the system-level structure of the proposed charge pump.

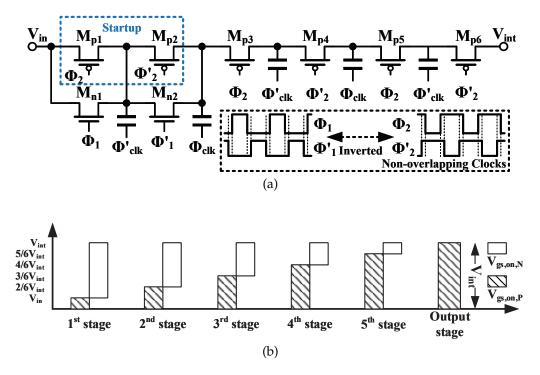

In Fig. 3.13(a), we present one phase of the proposed 5-stage linear charge pump for a detailed demonstration of  $V_{gs}$  optimization. For a 120 mV input voltage, a 600 mV output voltage is selected for the proposed 5-stage charge pump. Due to the low  $V_{DD}$  of the thermoelectric generator, we desire to operate the controller under a higher voltage to achieve the target speed and accuracy of the control loop. We select the output voltage, which is close to the threshold voltage, as the power source of the controller, following the general conclusion derived from the previous discussion.

Fig. 3.12. Charge pump structure.

Fig. 3.13. (a) Charge pump structure. (b)  $V_{gs}$  in different stages.

Fig. 3.13(b) shows the available  $V_{gs}$  at different stages. Since the output stage  $M_{p6}$  has sufficient voltage swing, using a standard threshold transistor could lead to improved efficiency because it reduces reverse leakage. However, the advantages garnered by employing a low-threshold voltage are restricted, as analyzed in the preceding sections. For the middle stages  $M_{p3}$ ,  $M_{p4}$ , and  $M_{p5}$ , which exhibit

Fig. 3.14. Minimal  $P_{s,sw}$  of each stage at different  $V_{gate,on}$ .

smaller  $V_{gs,on,P}$  due to source voltage shifts, we have chosen low-threshold voltage transistors with a threshold voltage of around 300 mV to compensate for the diminished  $V_{gs,on,P}$ . Despite the higher mobility of the NMOS transistor, it is not included in these stages because the PMOS transistor can offer leakage current prior to controller operation and is more suited for self-startup. Similarly, the first and second stages  $M_{n1}$  and  $M_{n2}$  utilize low-threshold voltage NMOS transistors to utilize the large  $V_{gs,on,N}$ . We have also incorporated additional small PMOS transistors  $M_{p1}$  and  $M_{p2}$  to provide currents during the startup process. Additionally, buffers for generating  $\Phi_{clk}$  and  $\Phi'_{clk}$  introduce more low-threshold NMOS transistors due to a gate driving voltage similar to the first stage, although this is not depicted in Fig. 3.13(a). To avoid latch-up, we bias the bulk of NMOS transistors to the ground, and similarly, bias PMOS transistors to  $V_{int}$ . Non-overlapping clocks,  $\Phi_1$ ,  $\Phi'_1$ ,  $\Phi_2$ , and  $\Phi'_2$ , are introduced to mitigate the effects of reverse leakage currents. The timing of  $\Phi_{clk}$  corresponds to  $\Phi_1$ , and  $\Phi'_{clk}$  aligns with  $\Phi'_1$ . Both  $\Phi'_{clk}$  and  $\Phi_{clk}$  have an amplitude of  $V_{in}$ . Even though the reverse biased  $V_{gs}$  in those stages during off-state can increase capacitive power losses due to larger voltage swings, it assists in reducing leakage currents. As suggested in [29], lowering leakage currents can enhance the efficiency of the charge pump.

In order to validate the impact of such gate voltage optimization, we simulated and plotted the power required to drive each switch under differing on-stage gate voltages  $V_{gate,on}$  for one phase. At a frequency of 250 kHz and 120 mV  $V_{in}$ , the output power reaches 180 nW. By activating the PMOS transistor with ground voltage and switching on the NMOS transistor with the output voltage, as observed from Fig. 3.14, we manage to prevent considerable power losses. Options for different threshold voltages sufficiently compensate for the source voltage shifts at each stage, ensuring an overall boost in efficiency. Although we can modify the gate voltage of transistors, particularly for  $M_{n1}$  and  $M_{p5}$ , without eliciting substantial power losses, using this voltage headroom (like activating  $M_{p5}$  with a 0.2 V on-state gate voltage) difference to lower the power consumption of the controller is challenging. This challenge occurs because the controller power needs to be sufficiently reduced while maintaining the speed and accuracy. If the  $P_{sw,c}$  is almost independent of the  $V_{gs}$ , it is not difficult to predict that driving the charge pump with a full swing would be the optimum choice. While further optimization may be possible, it demands innovative controller designs with presumably marginal benefits. This paper primarily focuses on balancing between controller and gate driving losses to enhance efficiency. Although it doesn't provide an optimization strategy for each transistor, it nonetheless provides a sufficient demonstration of the concept.

Regarding circuit design optimizations, the power conversion efficiency of the charge pump is a reflection of the efficiency of each stage. Therefore, any impact

Fig. 3.15. Controlled oscillator.

from scaling the transistor size will be evident in the overall charge pump power conversion efficiency, particularly under heavy load conditions. If the  $R_{on}$  exceeds its optimum value, the operating frequency will need to increase to counteract output voltage drops. This adjustment will continue until the  $R_{on}$  limits the output power and causes an output voltage regulation failure, subsequently leading to lower efficiency. If the  $R_{on}$  falls below its optimum value, take note that the charge pump frequency's lack of sensitivity to  $R_{on}$  when operating under SSL limits becomes important. In such cases, the system may suffer decreased power conversion efficiency due to losses induced by large switches. Therefore, such optimization is attainable within a few iterative attempts with the help of EDA tools.

#### 3.3.2 Controller

In the proposed design, frequency modulation is introduced to regulate the output. Fig. 3.15 illustrates the structure of the proposed controlled oscillator. The wide frequency modulation range and low power characteristics of delay gate-based ring oscillators have been proven in [27]. In this paper, to reduce leakage currents, two groups of delay gates with balanced PMOS leakage paths are used. These control

Fig. 3.16. Feedback loop for  $V_{fb1}$  and  $V_{fb2}$  generation.

Fig. 3.17. (a) Startup circuit (b) Startup process

the non-overlapping clock and frequency separately. The oscillator can be divided into three inverting stages, each consisting of two delay gates. For instance, in inverting stage 1, the delay gate, controlled by  $V_{b1}$ , dominates the delay of this stage. The delay gate controlled by  $V_{b2}$  dominates the delay for non-overlapping clocks. When  $V_{b2}$  is lower than  $V_{b1}$ , the current flows through the leakage path is larger, thus guarantee a shorter generated delay time. A proper non-overlapping control hence can be achieved. Overall, six phases are generated from the oscillator, which achieves ripple reduction.

Meanwhile, the circuits for generating  $V_{b1}$  and  $V_{b2}$  are shown in Fig. 3.16. A comparator compares the feedback voltage  $V_{fb}$  with the reference voltage  $V_{ref}$ , then generates clock signals on  $\Phi_{up}$  or  $\Phi_{down}$ . By controlling charge pump CP<sub>up</sub> and CP<sub>down</sub>,

the  $V_{b1}$  is directly generated at the holding capacitor  $C_h$ . For a better transient,  $V_{b1}$ is also coupled with  $V_{int}$ . By controlling  $V_{b1}$ , the frequency can be controlled, hence achieving output regulation. As speed is usually not the focus, ensuring the loop stability is not difficult. To follow the changes of frequency,  $V_{b2}$  also needs to follow the changes in  $V_{b1}$ . The  $V_{b2}$  are generated from  $V_{b1}$  using a reversed two-transistors voltage reference similar to [76]. By creating a constant voltage drop from  $V_{b1}$ , a proper non-overlapping period can be generated using  $V_{b2}$ . As the current flows through the leakage path in delay gates is small, the transistors for controlling the leakage path operate in the subthreshold region. Meanwhile, the voltage difference generated by the  $V_{b2}$  from  $V_{b1}$  is close to a subthreshold swing, the non-overlapping time hence is much smaller than clock periods. Maintaining the voltage difference between  $V_{b1}$  and  $V_{b2}$  hence results in a good ratio between clock periods and nonoverlapping times. It has to be mentioned here that the circuit performance is less sensitive to the variations of differences between  $V_{b1}$  and  $V_{b2}$ , the approach hence does not require calibrations. Moreover, during the startup process, M<sub>s</sub> would shunt the  $V_{b1}$  to  $V_{in}$ , which provides an initial bias for the delay gates.

#### 3.3.3 Startup Process

The controller, being powered by the output of the charge pump, necessitates a carefully designed startup process. In our proposed circuit, utilizing the leakage current for startup is a viable option. Therefore, additional startup circuits are introduced to manage this process and potential circuit failures, as shown in Fig. 3.17(a). During the startup process, transistor  $M_{isolate}$  isolates the external load and  $V_{int}$ . This action allows storage of charge into  $C_{int}$  and increases the voltage available to the controllers. Given that the oscillator can operate at a very low voltage, the accumulated charges at  $V_{int}$  can power the oscillator operation, which further pumps charges into  $V_{int}$ . With proper circuit design, the charges being pumped into  $C_{int}$

|                                      | 5-stage   | 3-stage   |  |

|--------------------------------------|-----------|-----------|--|

| Area mm( <sup>2</sup> )              | 1.924     | 1.170     |  |

| <i>C<sub>fly</sub></i> ( <b>p</b> F) | 30 * 50.4 | 18 * 50.4 |  |

| C <sub>int</sub> (pF)                | 46.6      | 46.6      |  |

| <i>C<sub>fb</sub></i> (pF)           | 2.12      | 2.12      |  |

**TABLE 3.1: Capacitor Parameters**

can exceed the controller's consumption, thereby leading to a successful startup. Isolating the load from the power converter during startup means that the startup process is determined by the circuit implementation. By calculating the clock cycle with a 6-bit asynchronous counter, sufficient startup time can be assured.

In case of circuit failure, this startup process needs to be activated if an unexpected drop is generated at  $V_{out}$ . In this design, the output voltage is the same as the controller supply voltage. By using both  $V_{out}$  and clocks as inputs to a NOR gate, the output status can be monitored. During normal circuit operations,  $V_{out}$  inhibits the input of clock signals, thereby locking the startup circuits. During circuit failure, characterized by a drop in  $V_{out}$ , the on-resistance of  $M_{isolate}$  increases, causing a voltage difference between  $V_{int}$  and  $V_{out}$ . Consequently, the asynchronous counter begins receiving clock signals, leading to the activation of the startup circuit. A summary of the overall startup process is presented in Fig. 3.17(b).

#### 3.3.4 Measurement Results