A Dissertation for the degree of

Doctor of Philosophy

# Successive-Approximation Based CMOS Process-Scalable Hybrid ADCs

Graduate School of Science and Technology

Keio University Keio University

YOSHIOKA, Kentaro

August 2019

## Abstract

Along with CMOS scaling, wireless/wireline communication performances have greatly advanced. To realize a system on chip (SoC) for such products, high-performance analog circuits are necessary; for example, high-speed and high-precision analog-todigital converters (ADCs) are often required to convert the received analog signal to digital. While such SoCs utilize the most leading CMOS technologies to cut down the costs of the digital circuits, the analog circuit performance inconveniently degrades as the CMOS scaling advance. To name an example, the Opamp gain performance greatly degrades with scaling with worsened transistor gain and lower supply voltages. On the contrary, as the communication standards further evolve, the performance demands toward analog circuits continue to increase. Thus, the design of ADCs in scaled CMOS process environments become one of the most challenging and critical fields of circuit design.

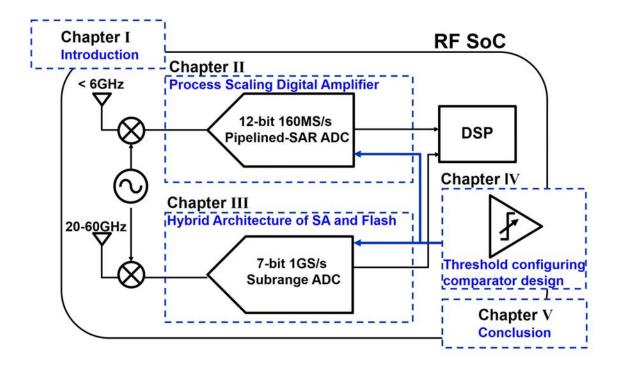

In this thesis, we aim to explore Hybrid ADCs utilizing successive-approximation (SA) circuitry, which can benefit from process scaling. And ultimately, we target to establish an ADC design methodology suitable for scaled CMOS technologies. In chapter 1, the technology trends of the CMOS process scaling are discussed and scaling effects to the analog circuitry are studied. Moreover, we show that SA circuitry is suitable for scaled CMOS and explore its limitations as well. Finally, recent research trends of Hybrid ADCs and its design challenges are discussed.

We propose a Hybrid ADC which heavily utilizes the SA circuitry in chapters 2 and 3. In chapter 2, the Digital Amplifier (DA) technique is proposed to realize power-efficient and accurate amplification in scaled CMOS which utilizes an SA

circuitry for amplification. DA cancels out all errors of the low-gain amplifier by feedback based on SA. Moreover, the amplification accuracy can be arbitrary set by configuring the number of bits of the DA; the amplifier gain is decoupled from the transistor intrinsic gain and brings in a new design paradigm for amplifier design in scaled CMOS. The fabricated ADC with DA achieves SNDR of 61.1dB, FoM of 12.8 fJ/conv., which is over  $3 \times$  improvement compared to conventional ADCs.

In chapter 3, we explore power-efficient and process scalable ultra-high-speed ADCs, required for high-capacity wireless communications. To achieve low-power and high-speed ADCs, we propose to dynamically configure the ADC architecture reflecting the ADC clock frequency, which we name Dynamic Architecture and Frequency Scaling (DAFS). The ADC architecture is reconfigured between successive-approximation and flash every clock cycle, relying on the conversion delay. A proto-type subranging ADC is fabricated in 65 nm CMOS, which is  $2 \times$  more power-efficient than the previously reported subranging ADCs.

In chapter 4, we propose a comparator with a variable threshold to explore multibit/step comparisons, which can significantly speed up the successive-approximation circuitry implemented in chapters 2 and 3. Finally, we establish a conclusion in chapter 5. ©

All rights reserved by Kentaro Yoshioka. August 2019.

## Acknowledgements

This thesis and the Ph.D journey was not available without the help of so many people, which I would like to acknowledge only a few.

First of all, I would like to show my largest gratitude to my advisor Prof. Hiroki Ishikuro. Entering the lab group, I hardly new anything about circuit design and researches but he led me up patiently and step-by-step. Interestingly, the first thing he taught us was Opamp design, and distilling that initial knowledge, Opamp design became the core part of this thesis. I would like to thank that he gave me various research opportunities, for a number of tapeouts and more on interacting with other research groups. The experience upon conducting researches with the Extremely Low-Power (ELP) group was very valuable, given feedbacks from industrial specialists. Also opportunities with collaborating with Fujitsu was very fortunate as well.

Not only Prof. Ishikuro taught me how to design circuits and publish papers at international conferences, but to enjoy and get most out of academic events as well (e.g. looking for the best local foods..). I really remember the first time when we visited the bay area for a conference (CICC), and Prof. Ishikuro set up opportunities to discuss with researchers at Apple, Stanford, UCB and imec. It was my first time interacting with top researchers overseas, and gave me high motivations to compete and collaborate with them in the near future. Recalling, those excitements led me to research experiences at Stanford over the following years as well.

I am very thankful to Prof. Tadahiro Kuroda, who initially taught me the spirit to challenge to top researchers and universities. When I was still a undergrad and deciding which department to proceed to, I heard Prof. Kuroda's talk which was about the journey upon competing with the world's top universities, and the importance of publishing researches at the premiere conferences (ISSCC). Such vision inspired me and drove my life towards Hardware design and researches.

I would like to thank my committee members, Prof. Nobuhiko Nakano and Prof. Tetsuya Iizuka who had generously taken their time for this Ph.D dissertation and would like to thank their guidance and advises to this thesis.

I would like to thank my lab members of Ishikuro/Kuroda group (just to name a few: Yuki Urano, Yuya Hasega, Teruo Jo, Atsutake Kosuge, Haruki Fukuda, Teturo Ogaki, Katuki Ohata) whom worked through countless sleep-less nights during number of tapeouts. I don't think any chip would have worked without their help and encouragements. Especially Dr. Akira Shikata helped me establish the knowledge of low-power SAR ADCs with his deep insights. Ryota Sekimoto and Takashi Chiba taught me patiently about the basics of data-converter designs.

I would like to show gratitude to members of the Extremely Low-Power (ELP) group, (especially Yasuyuki Hiraku and Isamu Hayashi) who passionately discussed and taught me basic flows and rules of IC designs. Also, I would like to thank members of Fujitsu Lab. (Sanroku Tsukamoto and Masato Yoshioka) who have given so many deep-insights of state-of-the-art ADC designs and various feedback to my research.

I would like to thank number of colleagues at Toshiba who have always given me generous supports. Firstly, Hirotomo Ishii, Tomohiko Sugimoto, Daisuke Kurose, and Naoya Waki have alwys been a respected analog designer, who taught me patiently about ADC design from the very basics. From them, I was able to learn how product-level design differs from research-level designs and what it is to become a professional analog designer.

Moreover, I would like to thank Masanori Furuta and Akihide Sai for mentoring through the research projects I have gone through at Toshiba RD. Industry driven researches differs greatly from academic researches, and I was able to learn a lot from the way they handled emerging research projects. Most of the researches within Toshiba would not have been accomplished at all if they were not my boss.

0.0

I would like to thank Prof. Mark Horowitz and his students for their generosity and kindness during my stay at Stanford. Mark patiently mentored me through the research I was going through, I would like to thank for his supportiveness. Learning the basics of computer architectures and hardware-software co-design was a great honor and simultaneously a great experience. Also I would like to thank Edward Lee, who had been an awesome collaborator at Stanford!

Last but not least, I would like to show great gratitude to my Mom and Dad, who have always been the most closest supporters of my researches and careers. I was very lucky given the amount of opportunities and generous educations they have given to me (including the 4.5 year life at the US), which is a key piece showing what I am now. I would also like to thank my partner Sayaka, who had been supportive both in both professional and private lives.

# Contents

| 1 | Intr | oducti  | on                                                        | 17 |

|---|------|---------|-----------------------------------------------------------|----|

|   | 1.1  | CMOS    | Scaling                                                   | 17 |

|   |      | 1.1.1   | Will CMOS scaling continue forever?                       | 18 |

|   |      | 1.1.2   | Recent trends in CMOS scaling and digital circuits        | 18 |

|   |      | 1.1.3   | Process scaling (and problems) with analog circuits       | 22 |

|   |      | 1.1.4   | Analog circuits' scaling effect                           | 25 |

|   | 1.2  | Towar   | ds process scalable analog circuits                       | 27 |

|   |      | 1.2.1   | Rise of SAR ADCs                                          | 27 |

|   |      | 1.2.2   | Fundamental Problems of the SAR ADC                       | 31 |

|   | 1.3  | Hybrid  | d ADCs                                                    | 32 |

|   |      | 1.3.1   | Pipelined-SAR ADCs                                        | 32 |

|   |      | 1.3.2   | Design challenges of the Pipelined-SAR ADC                | 33 |

|   | 1.4  | Thesis  | motivation and organization                               | 35 |

|   |      | 1.4.1   | Thesis organization                                       | 37 |

| 2 | Dig  | ital Ar | nplifier                                                  | 40 |

|   | 2.1  | Introd  | uction                                                    | 40 |

|   |      | 2.1.1   | Review of conventional amplifiers for scaled CMOS designs | 41 |

|   |      | 2.1.2   | Shortcomings of digital gain calibration                  | 42 |

|   |      | 2.1.3   | Our approach                                              | 44 |

|   | 2.2  | Digita  | l Amplifier                                               | 44 |

|   |      | 2.2.1   | Review of Opamp based amplifications                      | 44 |

|   |                    | 2.2.2          | Digital Amplifier Principles                                  | 46       |

|---|--------------------|----------------|---------------------------------------------------------------|----------|

|   |                    | 2.2.3          | Digital Amplifier Implementation                              | 47       |

|   | 2.3                | Furthe         | er Analysis of Digital Amplifier                              | 49       |

|   |                    | 2.3.1          | Amplification Error Characteristics                           | 49       |

|   |                    | 2.3.2          | Power Optimization Strategy                                   | 52       |

|   |                    | 2.3.3          | DA's opamp noise-canceling feature                            | 53       |

|   |                    | 2.3.4          | Spurious-free Characteristics of the DA                       | 54       |

|   |                    | 2.3.5          | Designing the SA range                                        | 56       |

|   | 2.4                | Pipelin        | ned-SAR ADC Architecture                                      | 57       |

|   |                    | 2.4.1          | Asynchronous Operation                                        | 58       |

|   |                    | 2.4.2          | Look-Ahead SAR Technique                                      | 58       |

|   |                    | 2.4.3          | Noise Budget                                                  | 59       |

|   | 2.5                | Circui         | t Implementation                                              | 61       |

|   |                    | 2.5.1          | Operational Amplifier                                         | 61       |

|   |                    | 2.5.2          | Comparator Designs                                            | 62       |

|   |                    | 2.5.3          | DA C-DAC Designs                                              | 64       |

|   | 2.6                | Measu          | rement Results                                                | 68       |

|   |                    | 2.6.1          | Scaling Effects of the Digital Amplifier                      | 72       |

|   |                    | 2.6.2          | Benchmarks                                                    | 72       |

|   | 2.7                | Conclu         | lsions                                                        | 73       |

| 3 | Dwr                | omic           | Architecture Configuring                                      | 75       |

| J | <b>Dy</b> I<br>3.1 |                |                                                               |          |

|   | 3.2                |                | nic Architecture and Frequency Scaling                        |          |

|   | 0.2                | 3.2.1          | Binary search (Successive approximation) and flash reconfig-  | 10       |

|   |                    | 5.2.1          | urable ADC                                                    | 78       |

|   |                    | 3.2.2          | DAFS operation                                                |          |

|   |                    | 3.2.3          | Analysis of DAFS                                              |          |

|   |                    | 3.2.3<br>3.2.4 |                                                               |          |

|   |                    | 3.2.4<br>3.2.5 | Metastability effects in DAFS ADCs         Offset calibration | 89<br>90 |

|   |                    | J.4.0          |                                                               | 90       |

|   | 3.3 | 7-bit S | Subranging ADC                                                                                                                                |

|---|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 3.3.1   | S/H and Folding Circuits                                                                                                                      |

|   |     | 3.3.2   | Live configuring with excess-delay accumulation 93                                                                                            |

|   |     | 3.3.3   | Metastability issues                                                                                                                          |

|   |     | 3.3.4   | Sub-ADC designs                                                                                                                               |

|   | 3.4 | Result  | s and Discussion                                                                                                                              |

|   |     | 3.4.1   | Measured Results                                                                                                                              |

|   |     | 3.4.2   | Discussions                                                                                                                                   |

|   | 3.5 | Conclu  | usions                                                                                                                                        |

| 4 | Thr | eshold  | Configuring Comparator 106                                                                                                                    |

|   | 4.1 | Introd  | uction $\ldots \ldots \ldots$ |

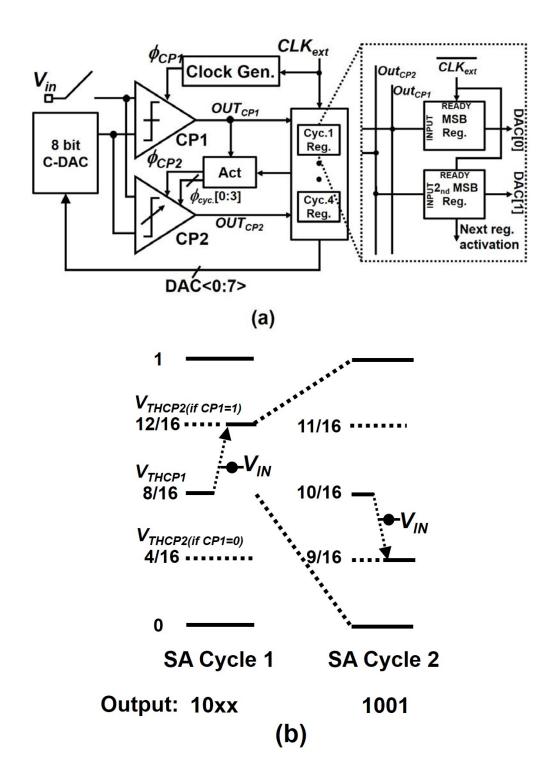

|   | 4.2 | 2-bit/2 | Step SAR ADC Architecture                                                                                                                     |

|   |     | 4.2.1   | Conventional Designs                                                                                                                          |

|   |     | 4.2.2   | 2-bit/step with threshold configuring comparators 109                                                                                         |

|   |     | 4.2.3   | 2-bit/step with Successively Activated Comparators 110                                                                                        |

|   |     | 4.2.4   | 2-bit/step with a single threshold configuring comparator 114 $$                                                                              |

|   | 4.3 | Wide    | range threshold configuring comparator                                                                                                        |

|   |     | 4.3.1   | TCC Architecture                                                                                                                              |

|   |     | 4.3.2   | TCC by variable current source                                                                                                                |

|   |     | 4.3.3   | Variable current source design                                                                                                                |

|   |     | 4.3.4   | Power Supply Noise Immunity                                                                                                                   |

|   |     | 4.3.5   | Temperature variation effects                                                                                                                 |

|   | 4.4 | Measu   | rement Results                                                                                                                                |

|   | 4.5 | Conclu  | usions                                                                                                                                        |

| 5 | Cor | nclusio | ns 132                                                                                                                                        |

|   | 5.1 | Summ    | uary                                                                                                                                          |

|   | 5.2 | Future  | e research directions                                                                                                                         |

| 5.2.1 | Further s | scaling | the I | DA | amplifier | (down | to | 16nm, | $7 \mathrm{nm}$ | and |       |

|-------|-----------|---------|-------|----|-----------|-------|----|-------|-----------------|-----|-------|

|       | beyond)   |         |       |    |           |       |    |       |                 |     | . 136 |

0.0

# List of Figures

| 1.1  | 42 years of processor trend. (In courtesy of [7] [8])                    | 19 |

|------|--------------------------------------------------------------------------|----|

| 1.2  | Apple A9 chip. (In courtesy of [13])                                     | 21 |

| 1.3  | Modern RF SiP integration                                                | 22 |

| 1.4  | Wireless performance trends                                              | 23 |

| 1.5  | FPGA with analog circuit integration (In courtesy of [22])               | 24 |

| 1.6  | SAR ADCs published in ISSCC, VLSI (1997-2008)                            | 27 |

| 1.7  | SAR ADCs published in ISSCC, VLSI (1997-2018)                            | 28 |

| 1.8  | SAR ADC circuit block diagram.                                           | 29 |

| 1.9  | Thesis organization.                                                     | 34 |

| 1.10 | Benchmark for high-speed high-resolution Pipelined ADCs                  | 35 |

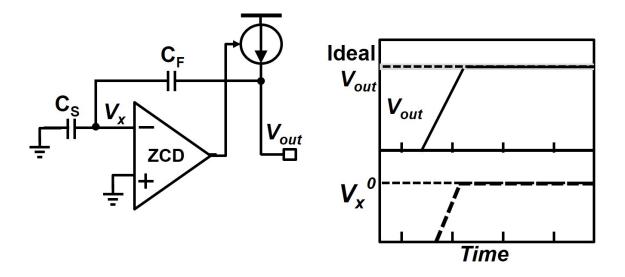

| 2.1  | Zero crossing based amplifiers                                           | 41 |

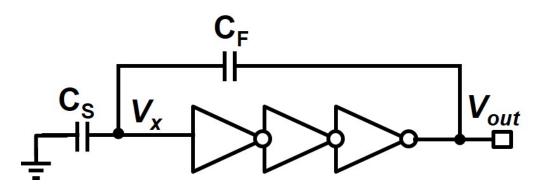

| 2.2  | Ring amplifiers                                                          | 42 |

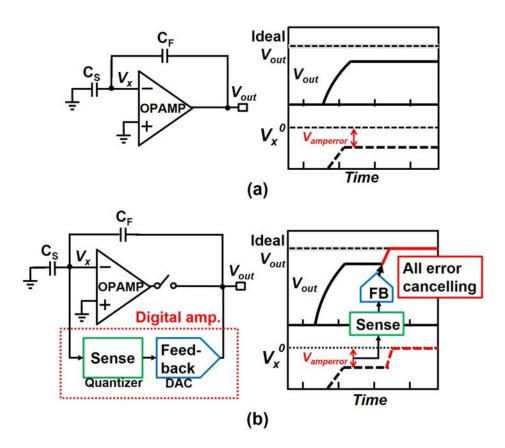

| 2.3  | (a) Amplification error due to the finite gain of opamps. A portion      |    |

|      | of the amplification error is observed at the virtual ground $V_x$ . (b) |    |

|      | Concept of the Digital Amplifier is shown. By directly sensing the $V_x$ |    |

|      | value and applying feedback to the output, digital amplifier cancels all |    |

|      | opamp-induced-errors (finite-gain, incomplete settling, thermal noise,   |    |

|      | etc.).                                                                   | 45 |

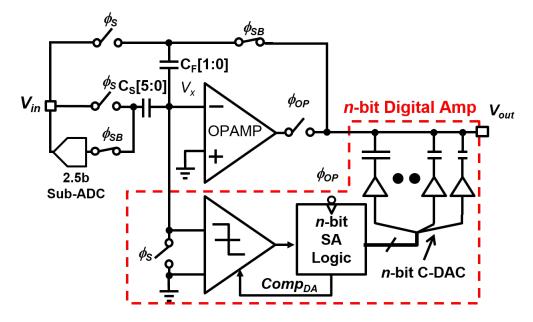

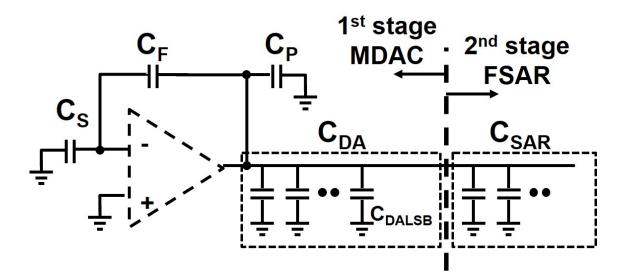

| 2.4  | Schematic of a 2.5-bit flip-around MDAC with $n$ bit Digital Amplifier.  | 46 |

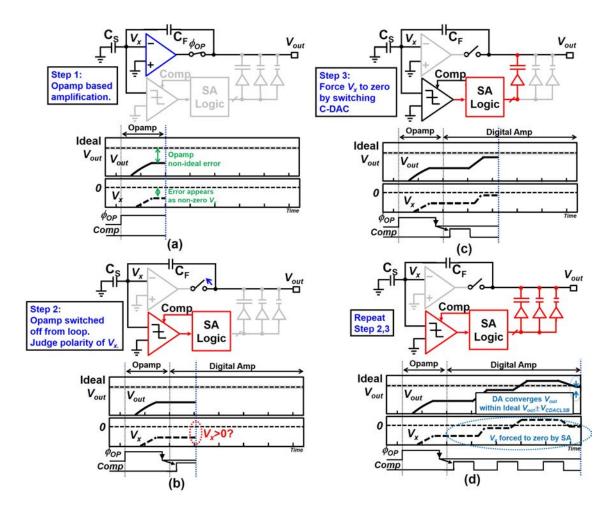

| 2.5  | Operation of the Digital Amplifier broken down in 4 steps. For sim-      |    |

|      | plicity, the DA is shown a 3-bit but the actual design is 8-bit.         | 48 |

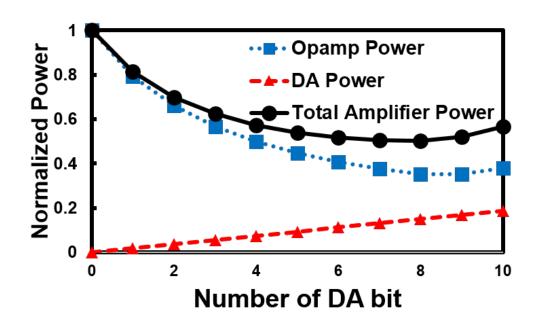

| 2.6  | Number of DA bit versus estimated MDAC power is plotted. 0-bit          |    |

|------|-------------------------------------------------------------------------|----|

|      | case is a MDAC designed only with an opamp. MDAC power starts           |    |

|      | to increase after DA's settling error mitigation effect saturates at a  |    |

|      | certain point.                                                          | 51 |

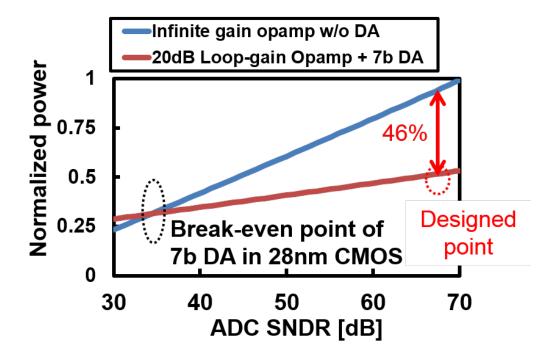

| 2.7  | We compare the power consumption of opamp-based and DA-based            |    |

|      | MDAC, respectively. Since DA-based MDACs has a relaxed settling         |    |

|      | requirements, at DA=7-bit, $46\%$ power savings can be expected at      |    |

|      | our target SNDR design point.                                           | 51 |

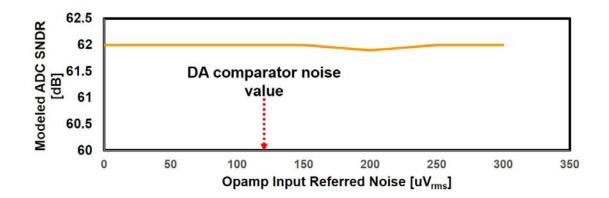

| 2.8  | The Matlab simulation results of the Pipelined-SAR ADC SNDR is          |    |

|      | shown, where the opamp noise is varied.                                 | 54 |

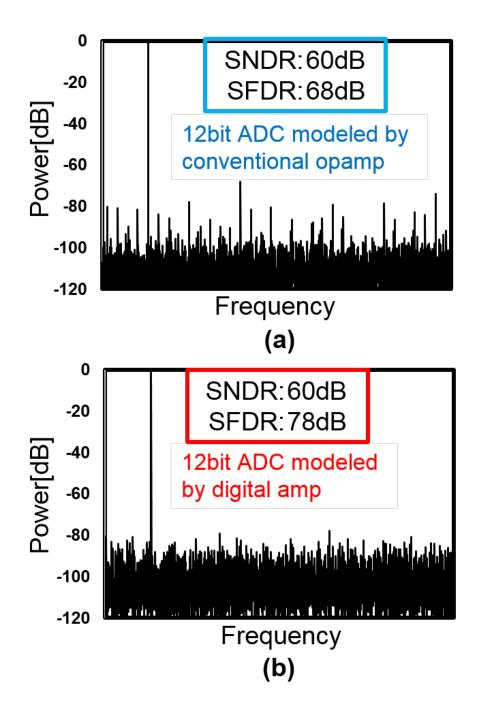

| 2.9  | Matlab simulated FFT results of the pipelined-SAR ADC are shown,        |    |

|      | where (a) uses opamp-based MDAC and (b) utilize DA-based MDAC.          |    |

|      | Since DA's gain error does not have correlation with the input signal,  |    |

|      | the SFDR excels by 10dB. Note that the opamp gain and DA bit were       |    |

|      | tuned to achieve the same SNDR.                                         | 55 |

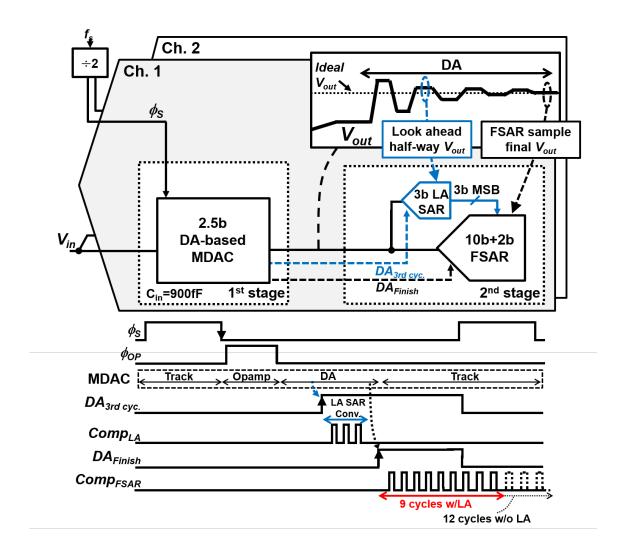

| 2.10 | The architecture of the two-way interleaved 12bit 160<br>MS/s pipelined |    |

|      | SAR ADC.                                                                | 57 |

| 2.11 | Noise contribution breakdown of the ADC                                 | 60 |

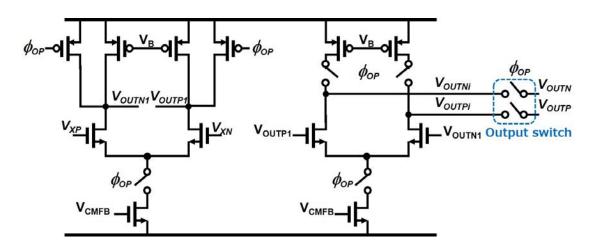

| 2.12 | Schematic diagram of the designed opamp.                                | 60 |

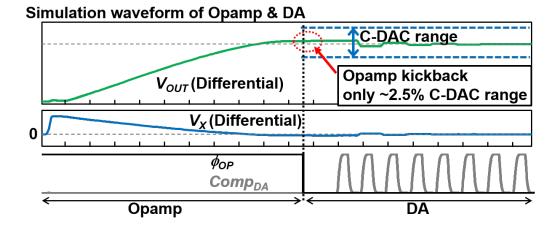

| 2.13 | Simulated waveform of the DA-based MDAC. While turning off the          |    |

|      | opamp causes kickback, the noise is small enough so that it can be      |    |

|      | canceled by DA operation.                                               | 61 |

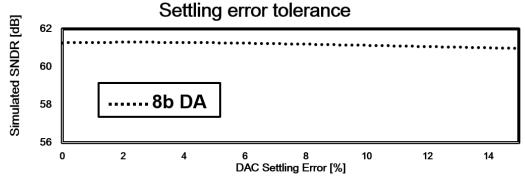

| 2.14 | DA C-DAC settling error versus ADC SNDR is shown. Since we              |    |

|      | utilize redundancy in the DA C-DAC, it is robust to settling errors     | 63 |

| 2.15 | Simplified figure of the ADC capacitor network.                         | 63 |

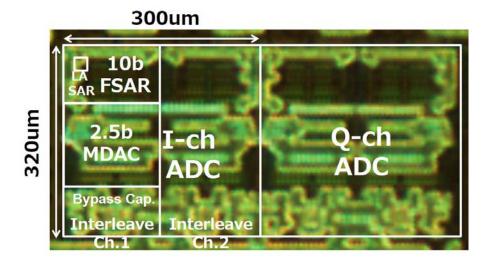

| 2.16 | Chip photo of the prototype ADC. Evaluation results of the I-channel    |    |

|      | ADC are shown.                                                          | 65 |

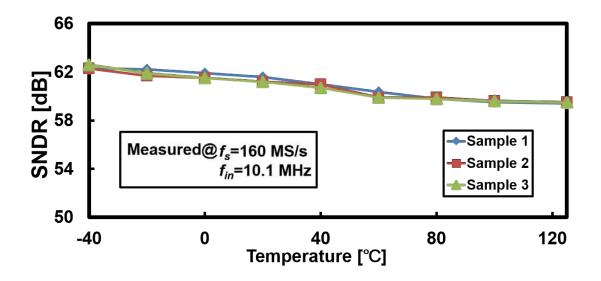

| 2.17 | ADC measured performance from 3 randomly selected chips. Tem-           |    |

|      | perature vs ADC SNDR were measured.                                     | 65 |

| 2.18                                                                        | ADC measured performance from 3 randomly selected chips. (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                  |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

|                                                                             | Measurement with varied $f_s$ (b) Measurement with varied $f_{in}$                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66                                                               |

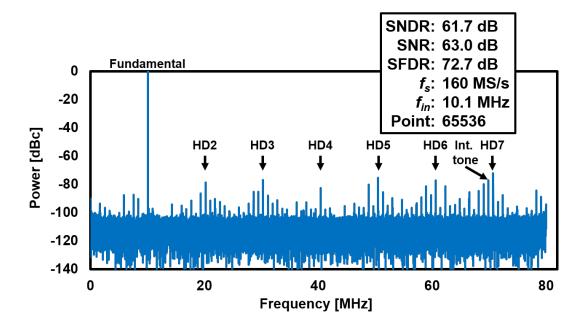

| 2.19                                                                        | ADC FFT measured results at $f_{in}$ =10.1 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67                                                               |

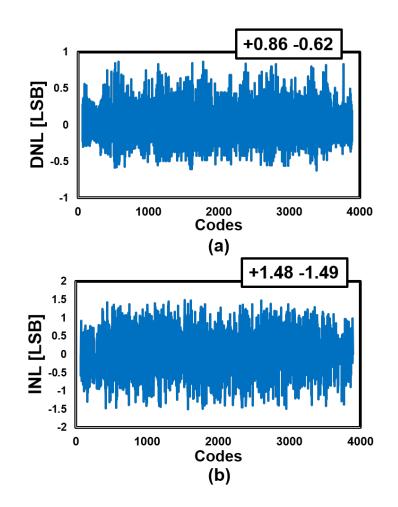

| 2.20                                                                        | (a) ADC measured DNL. (b) ADC measured INL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 67                                                               |

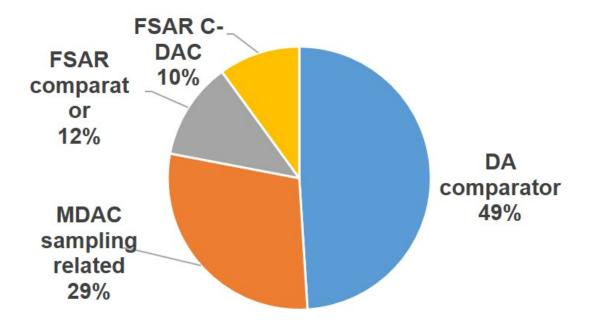

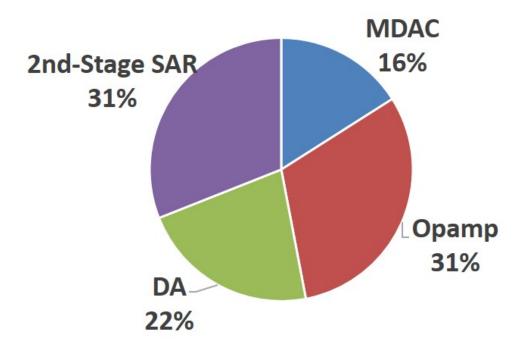

| 2.21                                                                        | Simulated power breakdown of the ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69                                                               |

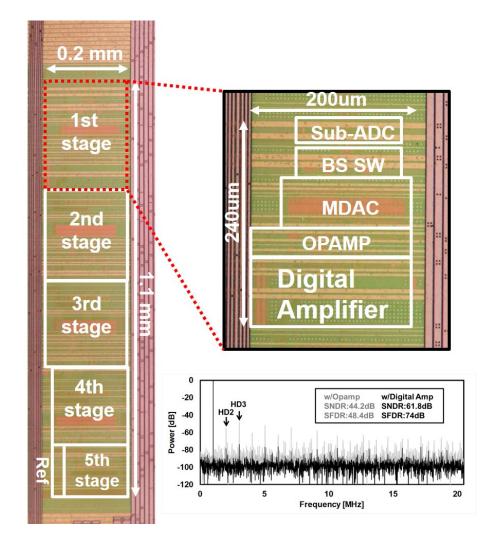

| 2.22                                                                        | A digital amplifier-based 11-bit pipelined ADC prototyped in 65nm                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  |

|                                                                             | CMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70                                                               |

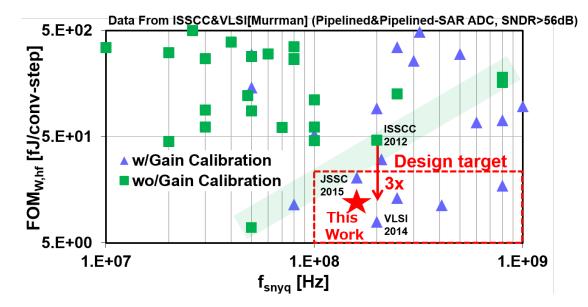

| 2.23                                                                        | Benchmark against Pipelined and Pipelined-SAR ADC published in                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |

|                                                                             | ISSCC and VLSI. Our work achieves $3 \times$ power efficiency improve-                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                  |

|                                                                             | ment compared to ADCs without gain calibrations                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73                                                               |

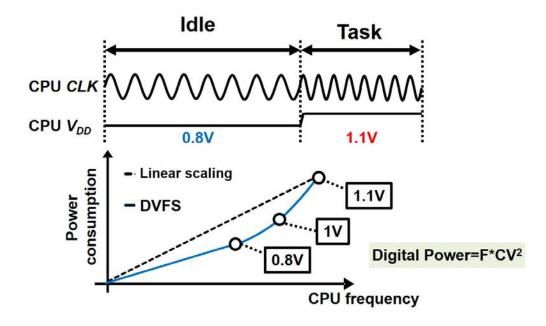

| 3.1                                                                         | Aggressive power scaling with DVFS, commonly utilized in CPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 76                                                               |

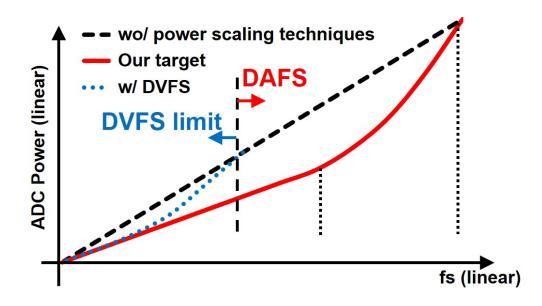

| 3.2                                                                         | Dynamic power scaling of an ADC without any power scaling tech-                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                  |

|                                                                             | niques, with DVFS, and with DAFS, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 77                                                               |

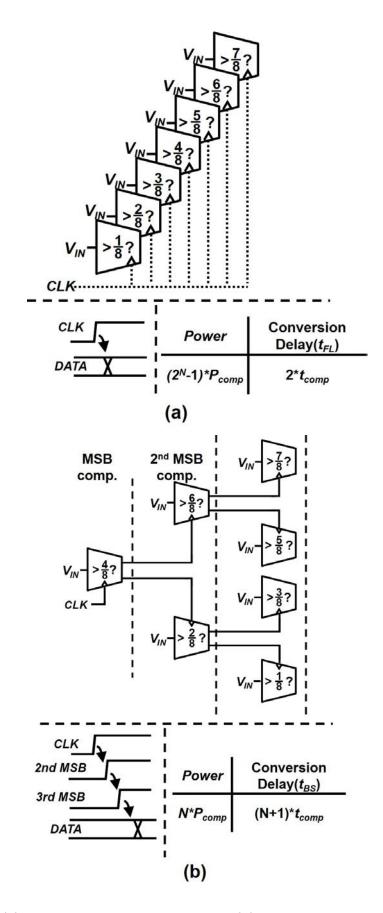

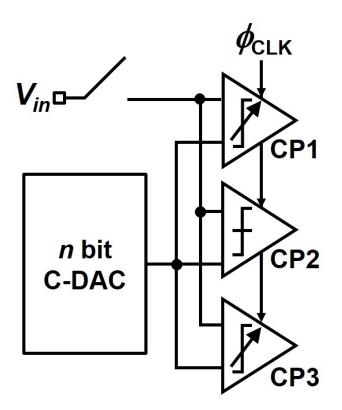

| 3.3                                                                         | (a) Schematic of 3-bit flash ADC. (b) Schematic of 3-bit binary search                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                  |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                  |

|                                                                             | ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79                                                               |

| 3.4                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 79                                                               |

|                                                                             | ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  |

|                                                                             | ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  |

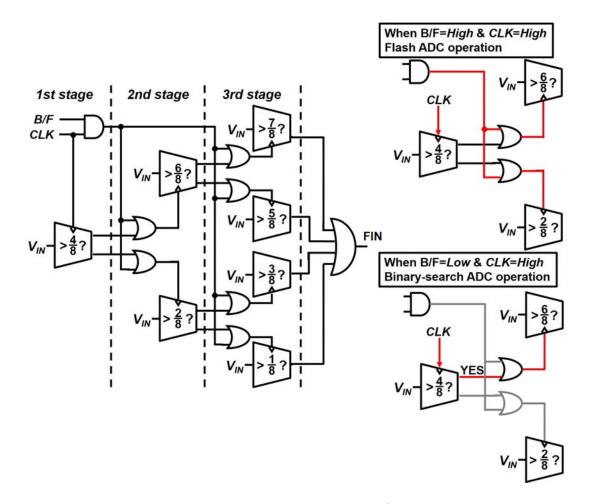

| 3.4                                                                         | ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82                                                               |

| 3.4                                                                         | <ul> <li>ADC.</li> <li>Schematic of the proposed binary search/flash reconfigurable ADC,</li> <li>realized by just adding OR cells to conventional Flash ADCs.</li> <li>(a) Simplified test bench with a 3-bit ADC using DAFS. (b) Timing</li> </ul>                                                                                                                                                                                                                                                             | 82                                                               |

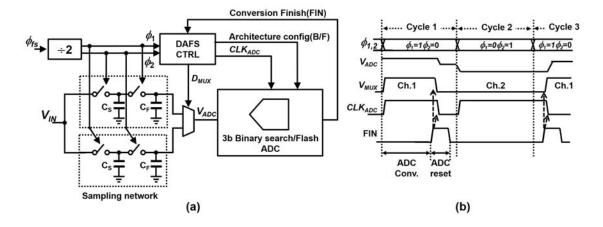

| 3.4<br>3.5                                                                  | <ul> <li>ADC.</li> <li>Schematic of the proposed binary search/flash reconfigurable ADC,</li> <li>realized by just adding OR cells to conventional Flash ADCs.</li> <li>(a) Simplified test bench with a 3-bit ADC using DAFS. (b) Timing</li> <li>chart showing the basic operation of the ADC.</li> </ul>                                                                                                                                                                                                      | 82<br>83                                                         |

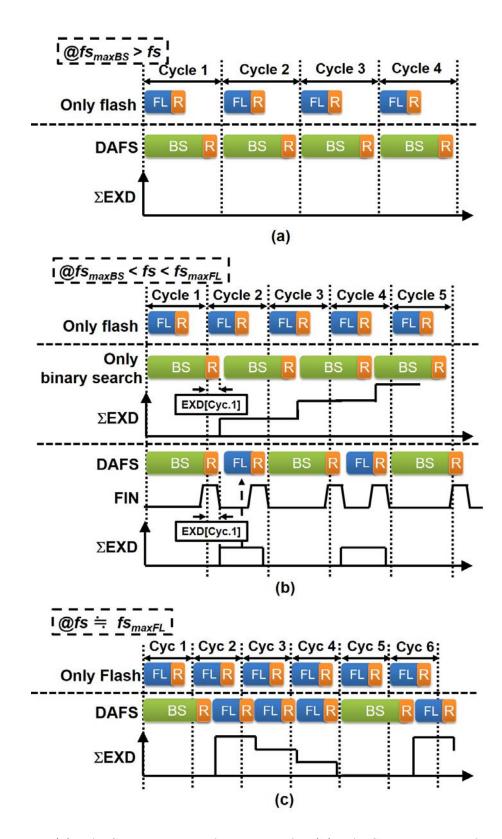

| 3.4<br>3.5                                                                  | ADC.<br>Schematic of the proposed binary search/flash reconfigurable ADC,<br>realized by just adding OR cells to conventional Flash ADCs.<br>(a) Simplified test bench with a 3-bit ADC using DAFS. (b) Timing<br>chart showing the basic operation of the ADC.<br>(a) DAFS operation at $fs_{maxBS} > fs$ . (b) DAFS operation at $fs_{maxBS} <$                                                                                                                                                                | 82<br>83                                                         |

| <ul><li>3.4</li><li>3.5</li><li>3.6</li></ul>                               | ADC.<br>Schematic of the proposed binary search/flash reconfigurable ADC,<br>realized by just adding OR cells to conventional Flash ADCs.<br>(a) Simplified test bench with a 3-bit ADC using DAFS. (b) Timing<br>chart showing the basic operation of the ADC.<br>(a) DAFS operation at $fs_{maxBS} > fs$ . (b) DAFS operation at $fs_{maxBS} < fs < fs_{maxFL}$ . (c) DAFS operation at $fs \simeq fs_{maxFL}$ .                                                                                               | 82<br>83<br>84                                                   |

| <ul><li>3.4</li><li>3.5</li><li>3.6</li></ul>                               | ADC.<br>Schematic of the proposed binary search/flash reconfigurable ADC,<br>realized by just adding OR cells to conventional Flash ADCs.<br>(a) Simplified test bench with a 3-bit ADC using DAFS. (b) Timing<br>chart showing the basic operation of the ADC.<br>(a) DAFS operation at $fs_{maxBS} > fs$ . (b) DAFS operation at $fs_{maxBS} < fs < fs_{maxFL}$ . (c) DAFS operation at $fs \simeq fs_{maxFL}$ .<br>Dynamic power scaling of an ADC operating only with flash and with                         | 82<br>83<br>84                                                   |

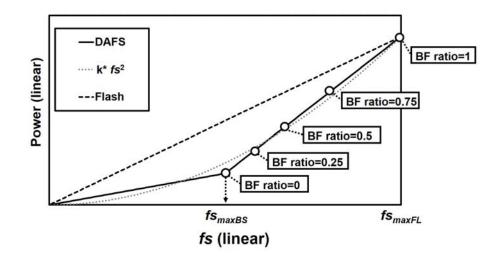

| <ul><li>3.4</li><li>3.5</li><li>3.6</li><li>3.7</li></ul>                   | ADC.<br>Schematic of the proposed binary search/flash reconfigurable ADC,<br>realized by just adding OR cells to conventional Flash ADCs.<br>(a) Simplified test bench with a 3-bit ADC using DAFS. (b) Timing<br>chart showing the basic operation of the ADC.<br>(a) DAFS operation at $fs_{maxBS} > fs$ . (b) DAFS operation at $fs_{maxBS} < fs < fs_{maxFL}$ . (c) DAFS operation at $fs \simeq fs_{maxFL}$ .<br>Dynamic power scaling of an ADC operating only with flash and with<br>DAFS, respectively . | 82<br>83<br>84<br>88                                             |

| <ul><li>3.4</li><li>3.5</li><li>3.6</li><li>3.7</li></ul>                   | ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82<br>83<br>84<br>88                                             |

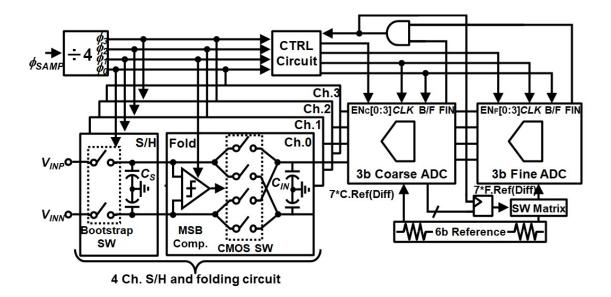

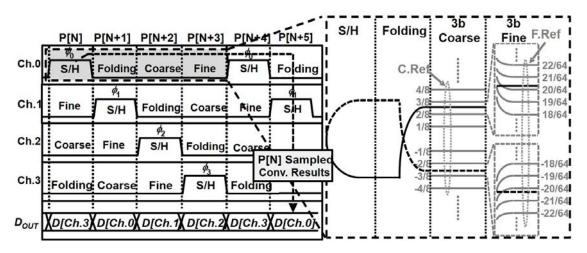

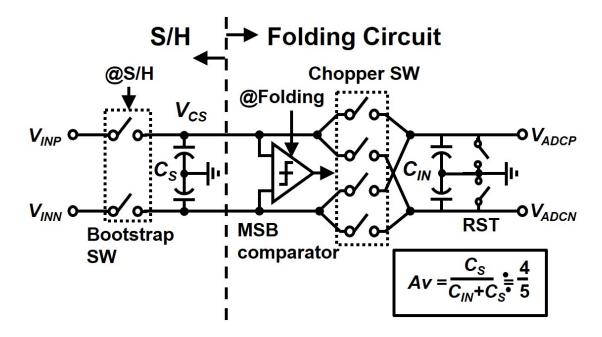

| <ul> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> <li>3.8</li> </ul> | ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul><li>82</li><li>83</li><li>84</li><li>88</li><li>91</li></ul> |

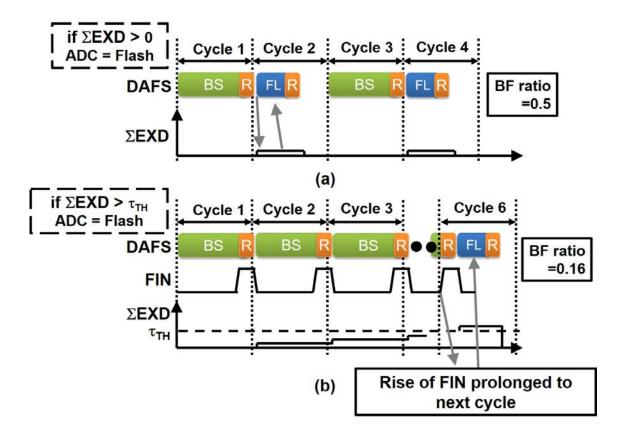

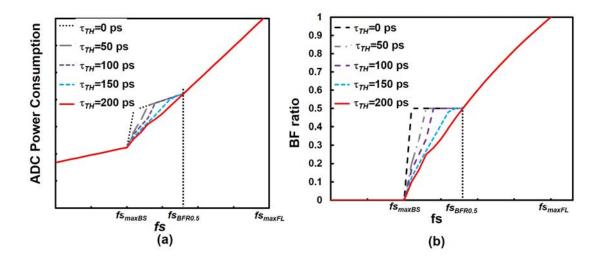

| 3.11 | (a) DAFS operation without $\tau_{TH}$ . Lowest BF ratio will be 0.5 since      |

|------|---------------------------------------------------------------------------------|

|      | flash operation will be inserted as soon as any EXD is detected. (b)            |

|      | DAFS operation with $\tau_{TH}$ . ADC does not switch to flash until exceeds    |

|      | $\Sigma$ EXD                                                                    |

| 3.12 | (a) Power scaling with several values of $\tau_{TH}$ . (b) versus BF ratio with |

|      | several values of $\tau_{TH}$                                                   |

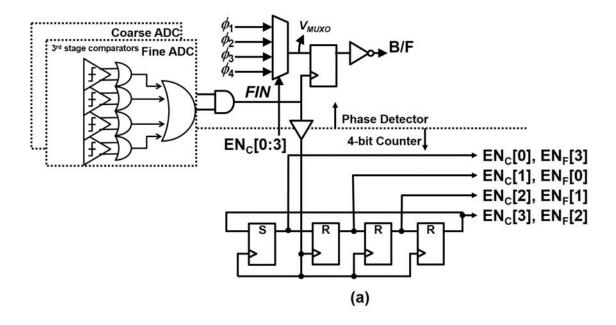

| 3.13 | Schematic of the live configuring circuit which uses the pulse length           |

|      | of FIN as $\tau_{TH}$                                                           |

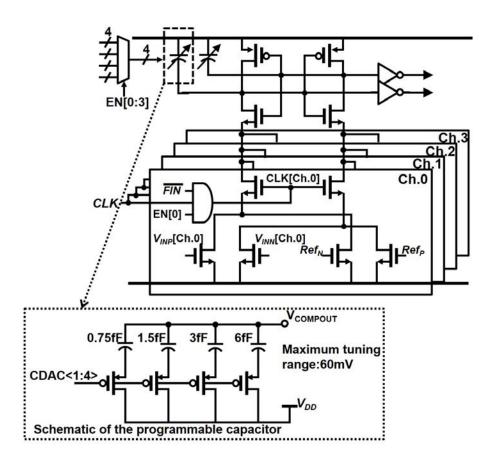

| 3.14 | Schematic of the comparator with four channel input. The input                  |

|      | channel is determined by signal $EN[0:3]$ . The programmable load               |

|      | capacitance used for offset compensation is shown as well 97                    |

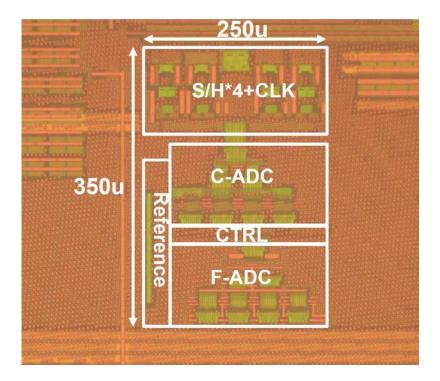

| 3.15 | Chip micrograph                                                                 |

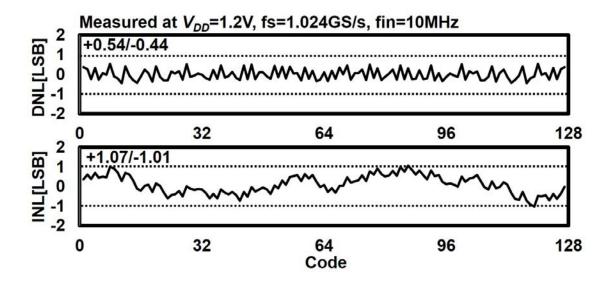

| 3.16 | Measured DNL/INL after foreground comparator offset calibration . $.\ 100$      |

| 3.17 | Measured power scaling of the subranging ADC, with and without                  |

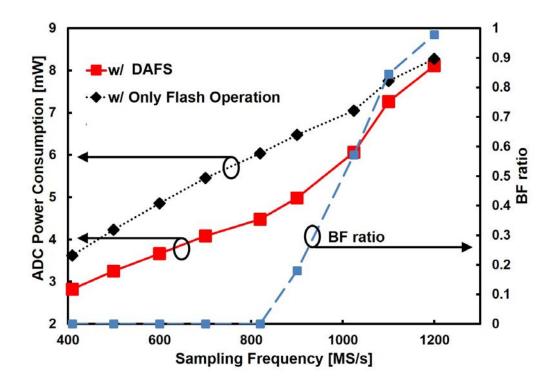

|      | DAFS. The BF ratio was measured and plotted as well 100                         |

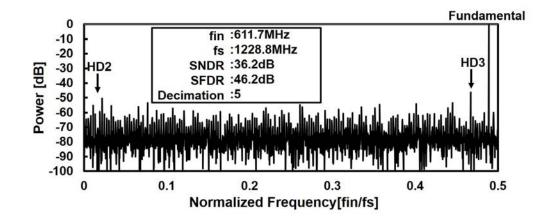

| 3.18 | Measured 4096-point FFT spectrum at the written condition 101                   |

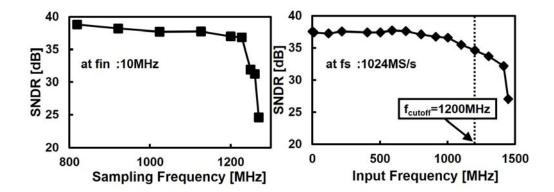

| 3.19 | (a) Measured versus SNDR. (b) Measured versus SNDR 102                          |

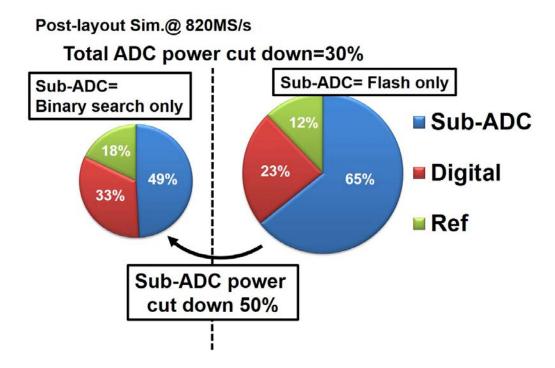

| 3.20 | Power breakdown of the ADC at 820 MS/s with sub-ADC operated $$                 |

|      | only with binary search and flash respectively                                  |

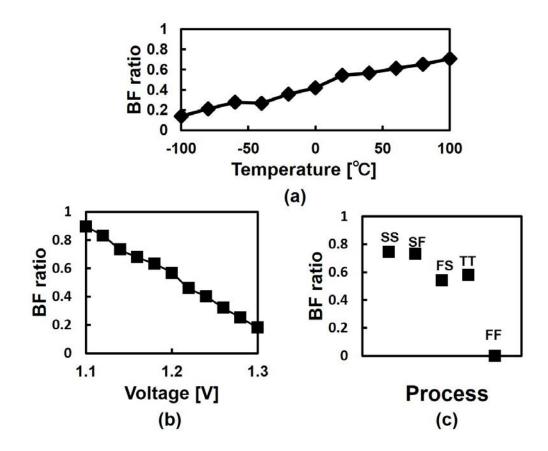

| 3.21 | PVT variations versus BF ratio is shown. Interestingly, DAFS can                |

|      | operate to cancel out PVT variation effects, relaxing the speed mar-            |

|      | gins of the high-speed ADC. (a) Temperature (b) Voltage (c) Process             |

|      | variations are plotted respectively                                             |

| 4.1  | Block diagram of a 2-bit/step ADC provided with TCC 109                         |

| 4.2  | Proposed 2-bit/step SAR ADC with successively activated compara-                |

|      | tors. (a) Block diagram. (b) Operation concept                                  |

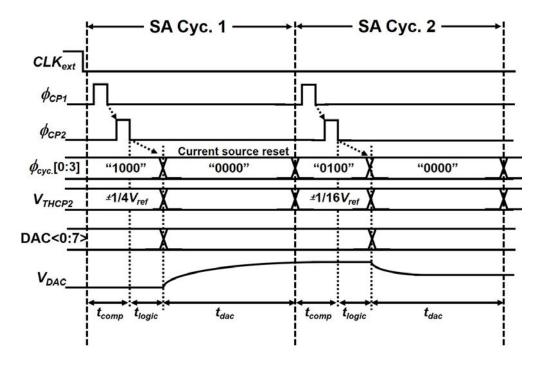

| 4.3  | Timing chart of the proposed ADC                                                |

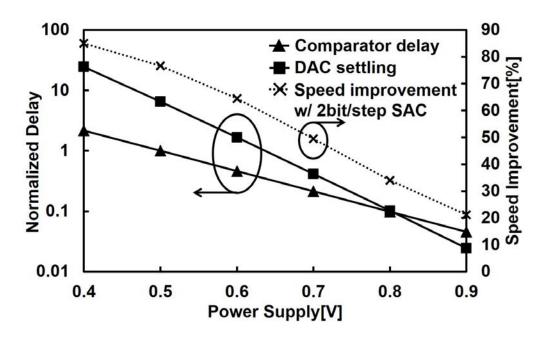

| 4.4  | Power supply versus comparator delay, DAC settling and speed im-                |

|      | provement respectively                                                          |

0.0

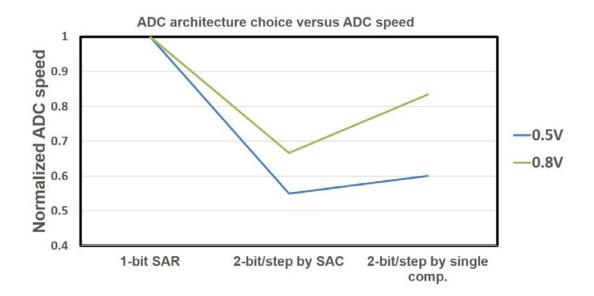

| 4.5  | ADC architecture choice versus ADC speed                                         |

|------|----------------------------------------------------------------------------------|

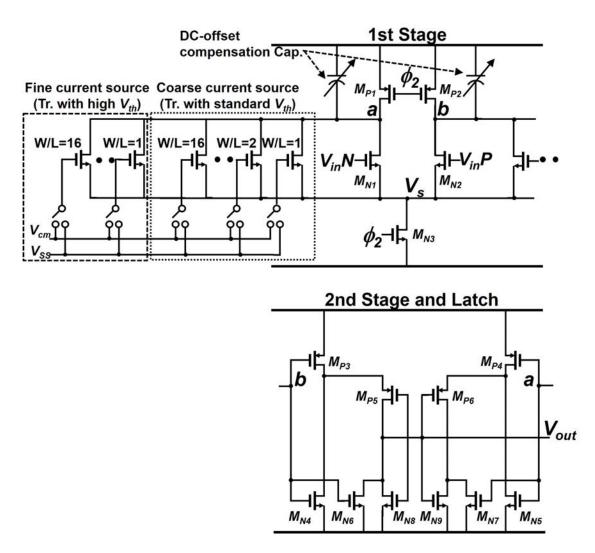

| 4.6  | Threshold configuring comparator design                                          |

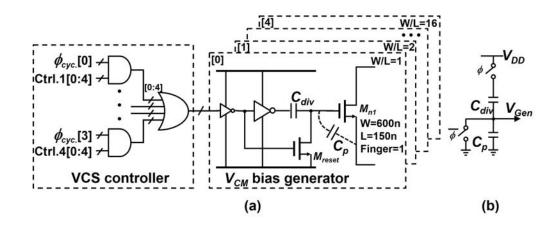

| 4.7  | (a) Schematic of 5-bit Vcm biased variable current source. (b) Oper-             |

|      | ation of capacitive dividing                                                     |

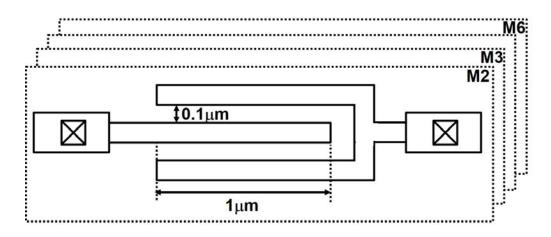

| 4.8  | Area efficient 1 fF fringed capacitor used to provide $C_{div}$                  |

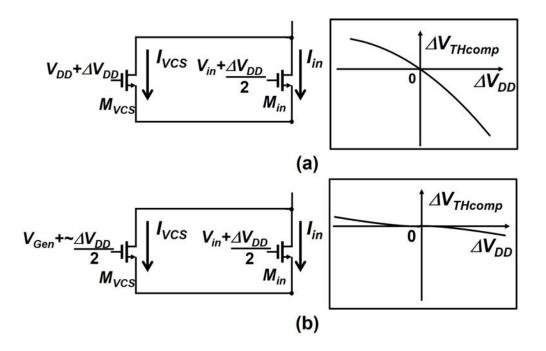

| 4.9  | Power supply variation effect of (a) $V_{DD}$ biased VCS, (b) $V_{CM}$ biased    |

|      | <b>VCS</b>                                                                       |

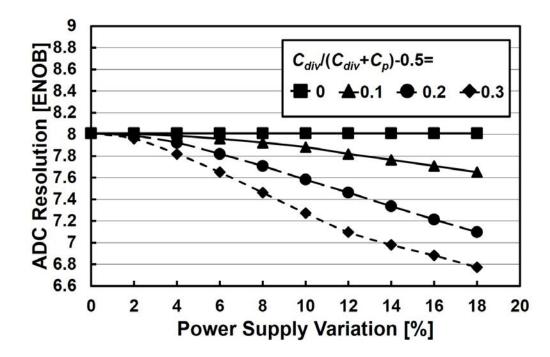

| 4.10 | Power supply variation versus ADC resolution with different settings. 123        |

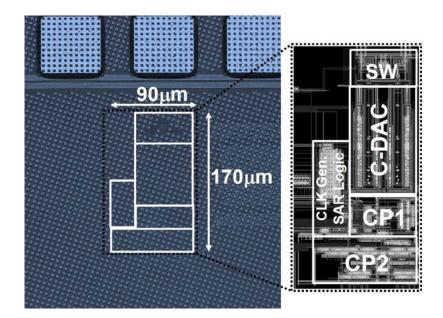

| 4.11 | Chip photo                                                                       |

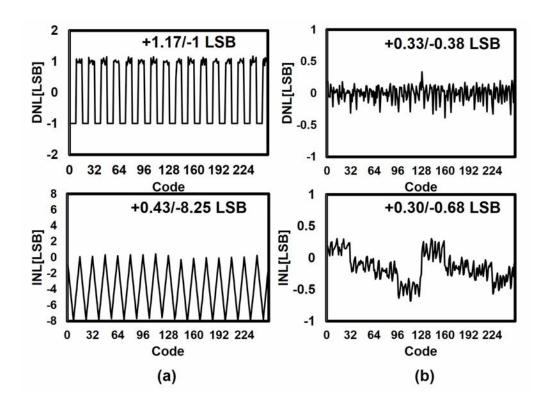

| 4.12 | (a)<br>DNL and INL before calibration at supply voltage of 0.5 V. (b)<br>DNL     |

|      | and INL after calibration at supply voltage of 0.5 V. $\ldots \ldots \ldots 125$ |

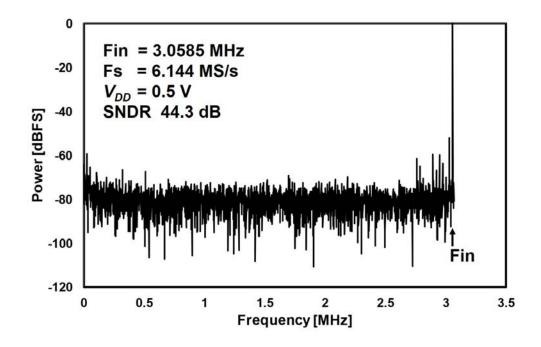

| 4.13 | FFT spectrum at condition shown                                                  |

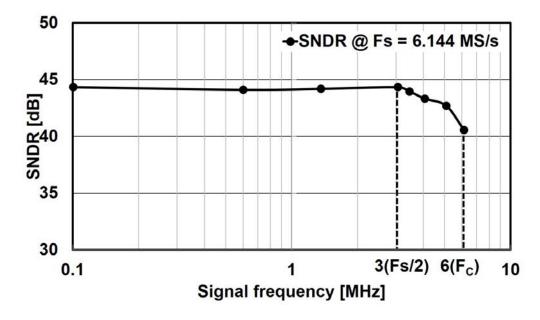

| 4.14 | Input signal frequency versus SNDR measured at 0.5 V                             |

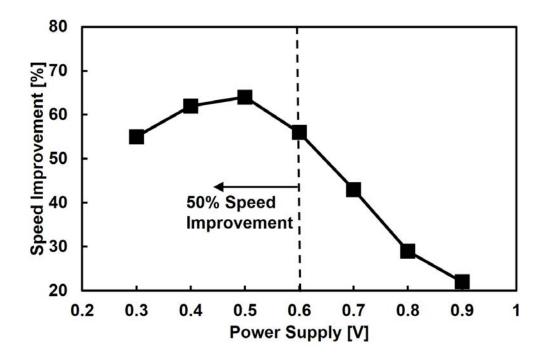

| 4.15 | Power supply voltage versus speed improvement by 2-bit/step SAC                  |

|      | operation                                                                        |

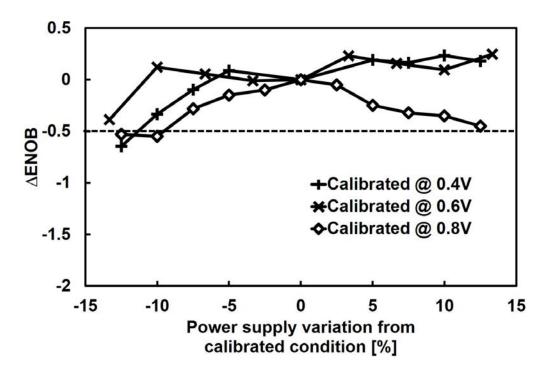

| 4.16 | Power supply variation versus ENOB response in several calibrated                |

|      | supply voltages                                                                  |

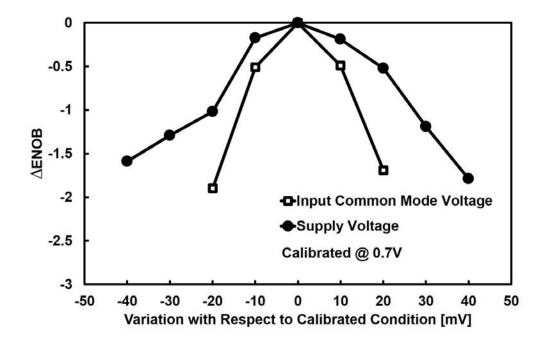

| 4.17 | Effect of power supply variation with Vcm or VDD changed separately $128$        |

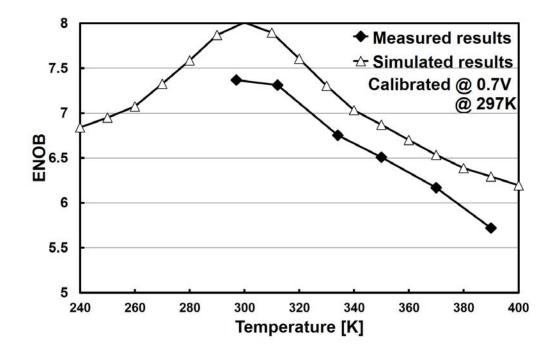

| 4.18 | Simulated and measured temperature variation effects                             |

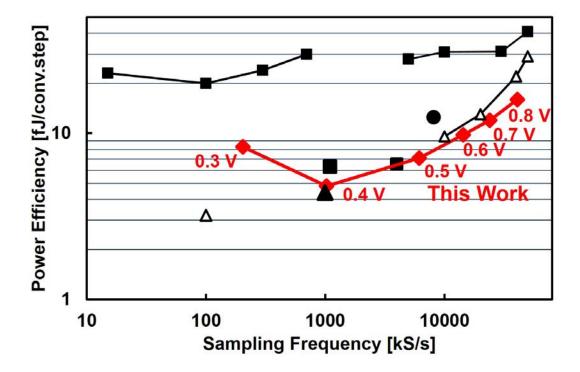

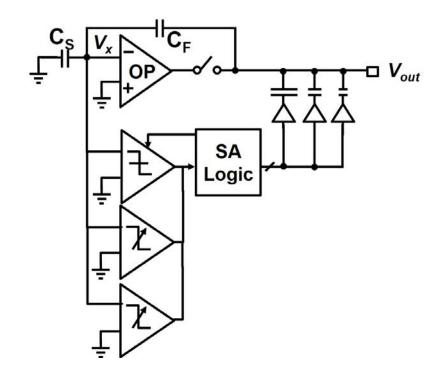

| 4.19 | Comparison with low power state-of-art works                                     |

| 5.1  | DA with 2-bit/step                                                               |

| 5.2  | DA estimated performance with 16nm and 28nm CMOS 136                             |

# List of Tables

| 2.1 | Normalized settling error requirements for opamp and DA based MDACs,  |

|-----|-----------------------------------------------------------------------|

|     | respectively                                                          |

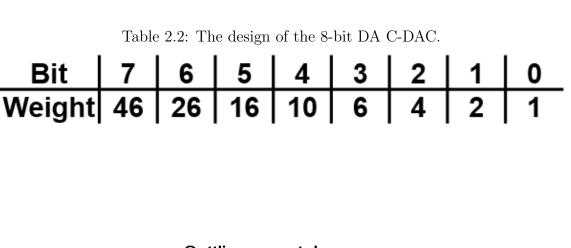

| 2.2 | The design of the 8-bit DA C-DAC                                      |

| 2.3 | Inter-process comparison of the digital amplifier-based MDAC 71       |

| 2.4 | Performance Comparison with state-of-the-art Pipelined and Pipelined- |

|     | SAR ADCs                                                              |

| 3.1 | Comparison with state-of-the-art high-speed ADCs                      |

| 4.1 | Comparison with conventional 2-bit/step ADC                           |

| 4.2 | ADC performance summary                                               |

## Chapter 1

### Introduction

### 1.1 CMOS Scaling

Since 1970 and until now, the number of transistors integrated with a single microprocessor has been continuously increasing. In 2019 today, the CMOS scaling continues; the 5nm CMOS risk production is soon beginning and developments of the next CMOS node (3nm CMOS) are highly active [1]. For example, the TSMC 5nm node brings 15% performance and 45% area improvements compared to the 7nm node [2]. 40 years ago, it has been said that the CMOS scaling limit is around 1um due to physical constraints (wavelength of light), but nearly  $1000 \times$  of scaling is about to be accomplished with a number of technology breakthroughs.

While the motivation towards CMOS scaling can be diverse, it is largely driven by economic and financial reasons. That is, by utilizing further scaled CMOS process, the unit cost of a single transistor can be cut down and the chip performance can be improved by moving to advanced CMOS process nodes. Therefore, a chip with more competitiveness and higher profit margins can be manufactured, which is the most important factor in silicon business. While CMOS fabrication companies (e.g. TSMC, Intel, Samsung, SMIC) invest an enormous amount of money and resource towards advanced CMOS processes and chip design companies invest largely on process porting, their expected ROI (return on investment) upon moving to the advanced nodes are much greater!

#### 1.1.1 Will CMOS scaling continue forever?

The end of CMOS scaling will approach when the amount of investment overcomes the expected return, which is expected to be the 3nm node or the next [3]. Then, what will happen to us circuit designers? Will we all lose our jobs? A potential technological direction is: for a specific application, a dedicated process technology may be adapted. Let us return to the point that the CMOS process is dominantly used because of economic reasons (it is far cheaper than using other processes!), even though existing other dedicated process technologies perform better than CMOS.

However, that precondition will be broken with further scaling and when CMOS cost stops scaling. Strong motivation will be born to adapt non-CMOS process technologies. For example, for RF SoCs, a co-integration of CMOS and compound semiconductors (GaNs, SiCs) can become the mainstream. For mobile SoCs where power consumption is crucial, SoI CMOS may be used. Co-integrating silicon photonics and CMOS is an interesting technology [4], which may produce breakthroughs in wireline communications[5] and LiDARs [6]. These multi-device integrations are exciting directions and will bring design paradigms even to analog circuit designs. Another optimistic technology direction is, the CMOS technology will cause a break-through (as it has done in the past decades) and process scaling will continue further on.

#### 1.1.2 Recent trends in CMOS scaling and digital circuits

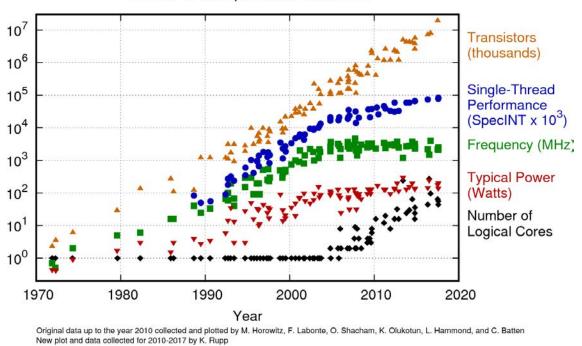

Let us return to the topic of the CMOS scaling trends. Fig.1.1 plots the processor performance of the last 42 years [7] [8]. While we say "scaling" in one word, the "Dennard's Law" scaling [9], which keeps the power consumption of the chip constant, has already ended and "Moore's Law" scaling [10] is the only one active, which simply increases the crammed number of transistors in a single chip.

When the "Dennard's Law" scaling was active, the device size and the clock frequency improved 30% every process generation. While this alone will explode the chip power, the entire power consumption of the chip was kept constant by scaling

42 Years of Microprocessor Trend Data

Figure 1.1: 42 years of processor trend. (In courtesy of [7] [8])

the power supply and the load capacitance. Note that while the load capacitance benefits from the physical scaling effect, the power supply voltage was scaled down by lowering the transistor's threshold voltage. However, "Dennard's Law" scaling ended around 2006 since the power supply voltage could no longer be turned down. Around this time, the transistor leak current (or off-currents) became a non-negligible power consumer in SoCs. Further scaling the transistor threshold voltage was difficult, since that will exponentially increase the leak currents.

After the Dennard scaling ended, the CMOS processors' performance becomes restricted by thermal density power (TDP) and not the clock speed. Chips cannot consume more power (or heat) than it can cool, or else the chip itself can be severely damaged if operated in high temperatures (> 125 deg.). One can notice the performance limitation by TDP when running a large program and monitoring the CPU clock rate; when the CPU temperature exceeds a certain amount, the CPU will configure to lower its clock rate, simultaneously degrading the processing performance. Thus, cooling technologies are highly active research areas in high-performance computing [11].

1.1

Interestingly, the inconvenience that the "Dennard's Law" scaling has ended became a strong motivation towards developing new digital circuit technologies. Conversely, when the Dennard scaling was active, the chip performance will greatly improve by just porting to a new process node; implementing new circuit technologies were not worth the try. One technology direction where the digital architectures head is "general" towards "domain-specific". For example, by looking at the number of logical cores in Fig. 1.1, we can tell that processors are heading to increase the operation parallelism and functionalities. While it is difficult to improve the performance of general single-instruction operations, multi-core processors boost the performance of highly-parallel operations and multi-task programs. Graphic processing units (GPUs) architectures evolved extremely in this direction. Stateof-the-art GPU has over 8000 cores [12] and has become the *de facto* standard for graphic processing and deep neural network training. While each core is simple compared to x86 cores, the enormous amount of parallelism becomes highly effective in "domain-specific" tasks like vector/matrix/tensor processing.

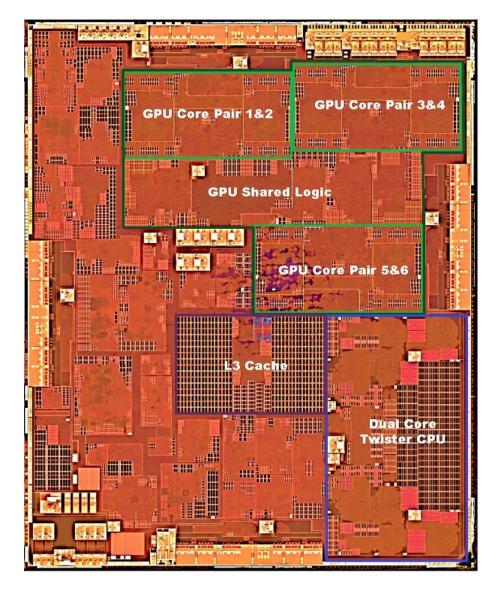

A number of processors utilize specialized hardware, given the extra number of transistors to be used. For example, smartphones have a very strict power budget and its processor power efficiency is top of mind. The iPhone A9 processor (Fig.1.2) has a dedicated CPU and GPU but also over 50 "specialized hardware" exist to process images, video, audio signals and to ensure extra user-security. Such "specialized hardware" can only perform a dedicated operation (e.g. encode video) but its power efficiency is extremely high compared to general processors. Moreover, dynamic voltage and frequency scaling (DVFS) techniques have become common in mobile SoCs to extremely scale power when the workload is small. To conclude, while performance improvements for general processors have hit the wall, "domain-specific" hardware has given rise. Interestingly, it can be interpreted economically that the investment return on architectures and technologies is now higher than investment in process technologies.

1.1

Figure 1.2: Apple A9 chip. (In courtesy of [13])

1.1

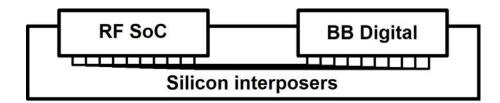

Figure 1.3: Modern RF SiP integration

#### **1.1.3** Process scaling (and problems) with analog circuits

Here, we will explain the analog circuit evolution trend in the last decade, compared to digital circuits. However, the largest problem in analog circuit design is that commonly, analog circuit performance degrades when moving to advanced nodes. We will study this effect further in the following sections. Generally, when we move to an advanced CMOS process node, we see that the analog circuit area scaling is much smaller than that of digital circuits. Therefore, the relative cost of analog circuits (per unit area) becomes higher and higher.

For some time, this impact on the SoC cost was neglected by the large cost scaling of digital circuits. However, the cost scaling of digital circuits has also become slower; it is becoming challenging to accept the increasing costs of analog circuits. In the latest smartphones (iPhone XS Max and Galaxy X released in 2018) [14] [15], the RF analog circuits and baseband digital circuits are separated to different chips. While splitting chips causes additional integration costs, we can infer that even with such integration costs, it has become more cost-efficient to get rid of analog circuits from the baseband digital chip.

However, applications such as mobile communications and high-speed IOs, which heavily utilize analog circuits, demand exponential performance improvement per product generation. To keep up with the pace of the performance improvements, the analog circuits must scale its area and performance as well.

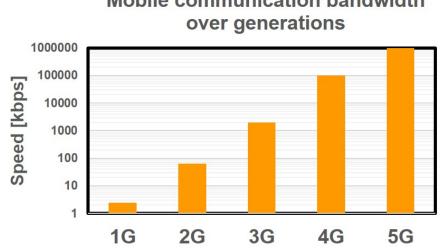

Fig. 1.4 shows the performance trend of mobile communication provided by the Third Generation Partnership Project (3GPP) [16]. During the 1G-2G-era, the communication speed was only a few kbps, which restricted the mobile phone applications to text data transferring. However, as it approached the 3G era, the

Mobile communication bandwidth

Figure 1.4: Wireless performance trends

maximum communication speed reached up to a few Mbps and opened up various mobile applications such as images, audio, and games. When the communication standards reached LTE and 4G, the speed evolved exponentially as well and opened up possibilities to even playing high-quality movie data via streaming. Nowadays, the 5G experimental services are beginning and its communication speed and capacity will evolve every year as well, even trying to reach a communication bandwidth of 100 Gbps [17]. 5G is seeking emerging applications given its excellent performance and potentials; for example, streaming all of the automobile's sensor data via 5G to realize a fully-autonomous vehicle controlled by cloud servers [18].

To further extend the evolution of wireless standards, high-performance analog circuitry are inevitable. Since mobile devices can not scale the battery capacity, the total hardware power consumption should score a par even with faster communication speeds. Otherwise, the mobile device battery life will degrade every time the wireless generation advances. To achieve this goal, the wireless circuit performance must track the CMOS scaling trends as well. Therefore, not only digital circuits but the analog circuitry must also scale its power efficiency along with CMOS process scaling; CMOS process scalable analog circuits are in high demand.

The analog circuits failing to scale are not a problem for wireless devices. For example, inter-processor and inter-server communication commonly utilize high-

Figure 1.5: FPGA with analog circuit integration (In courtesy of [22])

speed I/O circuits with ADC based receivers [19] [20]. CPU-GPU communication is done by PCIe busses and in the next generation (Gen.6 a.k.a PCIe 6.0), the PCIe standard requires PAM-4 based TX/RX to achieve 64 Gbps communication [21]. PAM-4 communications require high-performance ADCs and DACs operating at over 10 GS/s, which will largely dominate the IO performance and cost. Since CPU-GPU communication uses a  $16 \times$  link, at least 16 sets of ADCs are required in the IO circuitry. The ADC cost and performance must be extensively scaled to realize such a high-performance IO. While ADC-based transceivers have not been adapted for DRAM memory IOs yet, it may be replaced in the future if the bandwidth requirements continue to grow.

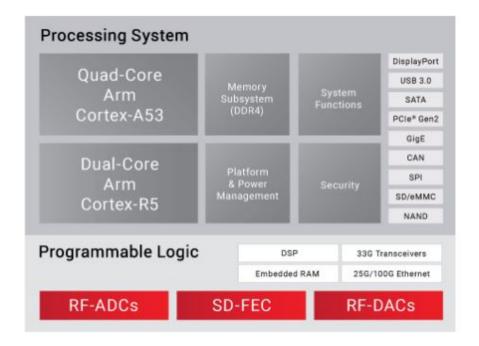

For a long time, ADC industrial researches were long driven by companies such as Analog Devices and Texas Instruments. However, such companies do not have a strong motivation to tackle into analog designs with advanced technology nodes because their main products are discreet analog devices and legacy nodes play along well. Recently, Xilinx drives researches of scaled CMOS analog circuits for highspeed I/Os and software-defined radios. Recent publications include > 4GS/s 13-bit ADCs in 16nm FinFET [23] [24] and integrated high-speed ADC based IOs [25]. By integrating the ADCs with the 16nm node, such circuits can be integrated within the FPGA (ZYNQ UltraScale + RF SoC is shown in Fig.1.5 [22]). For baseband stations with excessive numbers of MIMO, FPGAs integrated with multiple channels of high-performance ADCs can lower the system bill of materials (BOM) cost and power consumption, compared to the legacy implementation which integrates multiple discrete ADC chips.

#### 1.1.4 Analog circuits' scaling effect

Similar to digital circuits, can we take the analog circuit's scaling challenges as a step to revolutionize analog circuit designs? This thesis aims to establish an analog circuit design technique which is CMOS process scalable, especially focused on Nyquist ADCs. Before going to the details, we would like to study why analog circuits cannot compete with CMOS process scaling.

Here, we will focus on an operational amplifier circuit (Opamp), which is the key analog design components for multiple circuits (e.g. switched capacitor circuits, amplifiers, and filters). While there are multiple performance figures for an Opamp we will focus especially on: Gain-Bandwidth (GBW which couples with speed), output amplitude swings (which couples with noise), and lastly, gain (which couples with precision). To start, we will study the effect of scaling on each of the analog circuit performance measures. First of all, GBW improves with process scaling. Since the transistor GBW is decided by:

$$GBW = g_m/C_p \tag{1.1}$$

the parasitic capacitor  $C_p$  shrinks with scaling and GBW improves. On the other hand, the output swing is affected by the decreased power supply voltage. Therefore, it is essentially impossible to improve the output swing and is damaged by scaling. If the power supply decrease 10% by moving to an advanced node, relatively the analog circuit output swing, and noise performance will decrease *at least* 10%. Finally, we discuss the scaling effects to gain performance. The opamp gain is the most important factor upon obtaining high accuracy in pipeline ADCs. The adverse effects of scaling are most apparent in gain performance and are affected by both supply voltage drop and transistor analog performance degradation. Commonly, there are three approaches to achieve high-gain in Opamp design: 1.) cascode the transistors, 2.) increase the transistor W/L size to increase  $g_m$ , and lastly, 3.) increase the number of Opamp stages. A cascode configuration requires a voltage headroom of  $2V_{od} + 2V_{th}$ , the rest of the voltage margin is assigned to the output amplitude. However, let us expect  $V_{th} = 0.4V$ ,  $V_{od} = 0.1V$  and power supply voltage 0.9V in 28 nm CMOS technology. Critically, with cascoding, the voltage headroom alone reaches 1V, exceeding the power supply voltage. While Opamp gain can be enhanced by increasing  $g_m$  and the number of stages, such approaches consume much more power than cascoding.

Another problem in scaled CMOS analog circuit design is the degraded performance of the transistor itself. As well known, with a sufficiently large output resistor, the gain of a common source amplifier circuit can be derived as

$$Gain = g_m \times r_o \tag{1.2}$$

1.2

where  $r_o$  is the output resistance of the transistor. While  $r_o$  directly couples to gain, the value of  $r_o$  is an inverse proportion to the channel length (L) and utilizing scaled transistors will damage the Opamp gain. While we can obtain sustainable  $r_o$ by venturing the use of large L, this approach cannot gain any benefits from process scaling; the relative cost of analog circuits will eventually increase.

26

1.2

Figure 1.6: SAR ADCs published in ISSCC, VLSI (1997-2008)

### 1.2 Towards process scalable analog circuits

#### 1.2.1 Rise of SAR ADCs

On the other hand, there also exists an analog circuit whose performance improves by process scaling. A typical example is the SAR ADC. Conventionally, SAR ADCs were utilized for low speed, high-resolution ADCs due to their nature which requires multiple successive approximation (SA) cycles to complete the conversion. Typically, the number of required SA cycles is equivalent to the number of state bits. On the other hand, Pipelined and Flash ADC's conversion time is overwhelmingly short and have been adapted for high-speed applications. For example, in the case of Flash, the conversion delay is similar to that of a single comparator delay. The pipeline ADC's conversion delay consists only of a sub-ADC conversion and signal amplification, naturally suiting high-speed applications. However, all circuit blocks of the SAR ADC benefit from scaling and its performance have improved along with CMOS scaling. Due to that fact, the SAR ADC's performance improvement over the last decade was remarkable and looking back at the history of published SAR ADCs in the last two decades is very informative.

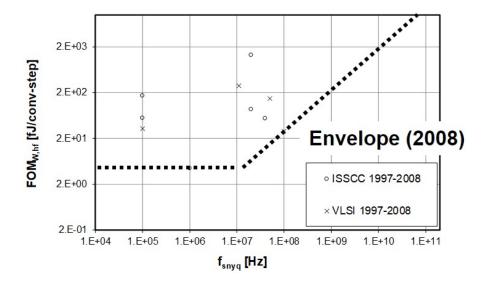

Fig.1.6 plots the SAR ADC performance published in ISSCC and VLSI during 1997-2008, whose data are based on [26]. The x-axis shows the sampling speed and

Figure 1.7: SAR ADCs published in ISSCC, VLSI (1997-2018)

the y-axis shows the Walden figure of merit (FoM) [27]. During those days, the most advanced process node was 65nm CMOS and most of the works were based on 130nm or 180nm CMOS. To plot the evolution of unit-SAR ADC performances, we exclude time-interleaved ADCs in the plot, whose fastest unit SAR ADC was 100MS/s. The Elzakker SAR ADC [28] was presented at ISSCC 2008 (is included in the plot), which improved the SAR ADC power efficiency by  $10 \times$  (!) compared to the prior art. This work showed one shape of an "accomplished" SAR ADC, which gave rise to extensive researches upon further improving the SAR ADC performance and is still active until now.

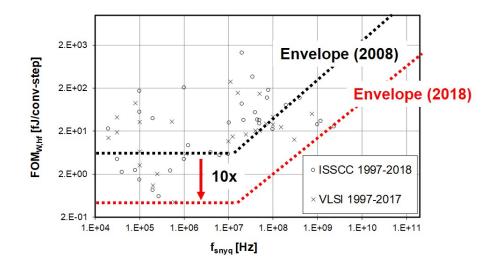

Fig. 1.7 shows the SAR ADC performance presented during ISSCC and VLSI until now (1997-2018) [26]. Firstly, the process technologies evolved greatly in the past ten years, and the most advanced node presented was 14nm CMOS.

Let us study the evolution in both terms of speed and power efficiency. The SAR ADC research direction splits into mainly two paths: those that pursue power efficiency at low speeds (< 1MS/s) and those that pursue high-speed, high-resolution performance aiming to replace Pipelined ADCs. For the former, the power efficiency was further pushed and reached even 0.4fJ/conv., mainly due to the optimization (supply voltage were reduced from 1V to 0.3V, which improves the energy efficiency 10×) and improved process nodes. Therefore, the SAR ADC energy bounds were

Figure 1.8: SAR ADC circuit block diagram.

pushed nearly  $10 \times$  in the past 10 years, which are beneficial to realize low-powered and high-precision sensor devices for IoT systems. Interestingly, many SAR ADCs that achieve > 10-bit and high-speeds (> 100MS/s) have also been published and is an active research area. Since > 100MS/s ADCs are mandatory for mobile communications (LTE and WiFi), power-efficient SAR ADCs replacing the power-hungry Pipelined ADCs are in high demand. The speed boundaries have also been pushed  $10 \times$ , which greatly expanded the application of SAR ADCs.

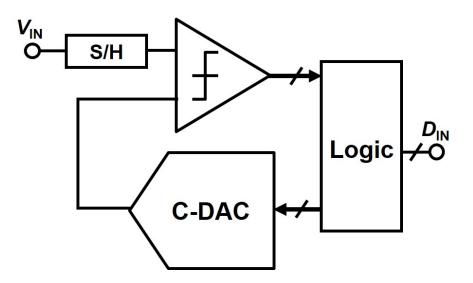

Before going into the further details of the SAR ADC, the fundamental SAR ADC operation is explained briefly. The block diagram of the *n*-bit SAR ADC is shown in Fig. 1.8. After sampling the input signal  $V_{in}$ , the comparator compares either the input or the reference voltage is larger. The reference voltage utilized during the comparison is generated by the C-DAC, which has a resolution of *n*-bit as well. Since C-DAC is the only analog (in terms of having multiple voltage levels) component in the ADC, the ADC linearity is determined by this circuit. The comparison result is stored in the logic circuit, and the reference voltage is shifted in the direction in which the input range can be narrowed down. The SAR ADC operation is binary search: during the initial comparison (or MSB cycle), the SAR ADC configures if the input signal is larger than  $1/2 V_{ref}$  or not. If the input signal is smaller, the reference voltage will be shifted to  $1/4 V_{ref}$  and if larger, the reference

voltage will be configured to  $3/4 V_{ref}$ . The procedure above is one cycle, and by repeating for the given number of cycles, fine analog-to-digital conversion results are obtained.

Next, we will review the function of each circuit in the SAR ADC and consider the impact of process scaling. Fundamentally, the SAR ADC cycle time can be represented by the sum of the delays of the comparator, logic, and C-DAC, as shown bellow.

$$Cycle = t_{Comp} + t_{Logic} + t_{CDAC} \tag{1.3}$$

First of all, the process scaling effect appears most straightforwardly in logic circuit delays. Since the SAR ADC's logic circuit is mainly composed of flip-flops, the delay of the logic is almost equivalent to the digital gate delay. Therefore, similar to a general digital circuit's scaling effect, the delay will be 30% faster for every time the process node advance.

Also, comparators benefit from scaling and the speed will improve proportionally to the GBW and digital gate delay. In general, the comparator circuit can be divided into two circuits, a preamplifier circuit that converts the voltage difference between two inputs into a current difference, and a latch circuit that will amplify the current difference and output as a digital value. The delay of the latch circuit corresponds to the digital gate delay, similar to  $t_{Logic}$ . The speed of the preamplifier circuit corresponds to the transistor GBW, which also improves with process scaling.

Also,  $t_{DAC}$  is proportional to the unit capacitance of the C-DAC. In legacy process technologies, capacitors were created by inserting insulators between vertical metal layers (metal-insulator-metal MIM capacitor). While MIM capacitor has a superior matching property, the minimum capacitance is quite large (10-50fF). On the other hand, advanced process technologies enable the use of metal-oxide-metal (MOM) capacitors, which simply utilize the parasitic capacitance born between metals. Since the metal fabrication accuracy has improved significantly, it has become possible to create highly accurate capacitors. Because MOM capacitors can utilize very small unit capacitance (down to 500aF), the energy consumption and the delay of the C-DAC has greatly improved together with developments of efficient C-DAC switching techniques [29].

1.2

#### **1.2.2** Fundamental Problems of the SAR ADC

Although the SAR ADC has made a performance breakthrough in the past decade, the performance enhancement has hit a brick wall. We will study this further in this section. As a rule-of-thumb, realizing a high-resolution and high-speed SAR ADC is challenging. In this section, we will analyze some fundamental reasons behind this.

One of the challenges which SAR ADCs face is the reference voltage settling constraints. Due to the structure of the binary C-DAC, when the large MSB capacitor is switched after the first comparison, a large amount of charging/discharging occurs. Such sudden charge fluctuation causes ringing in the reference voltage, because of the LC resonance of the bonding inductance. To obtain high accuracy by the SAR ADC, such voltage ringing must be attenuated within < LSB/2 to LSB/4, since fluctuated reference voltage corrupts the conversion accuracy. Since a typical solution is to simply "wait" until the ringing calms down, this prolongs  $t_{C-DAC}$  and limits the conversion speed.

One way to reduce the voltage ringing is to utilize a large "decoupling" capacitor on-chip so that sufficient amount of charge can be supplied on-chip. However, such decoupling capacitors can easily reach few nFs [30] [31] to achieve high-accuracy. Such capacitors can be even several times larger than the ADC core, and its cost overhead may not be acceptable for low-cost mobile SoC applications.

Another way to get around the voltage settling is by providing an on-chip voltage buffer. With a sufficient buffer bandwidth, we can suppress reference voltage fluctuations. On the other hand, this breaks the premise that SAR ADCs do not require an active element; voltage buffers are a high-bandwidth power-hungry opamp. While the power consumption of the voltage buffer is typically excluded in the ADC performance presented at academic conferences, some works report that the utilized voltage buffer itself consumes  $4\times$  more power than the SAR ADC itself [32]. If the SAR ADC included the voltage buffer in its core area, most high-speed high-resolution SAR ADCs may even under-perform the power efficiency of stateof-the-art Pipelined ADCs.

### 1.3 Hybrid ADCs

As mentioned in the previous section, it is fundamentally difficult to realize a highresolution and high-speed SAR ADC. On the other hand, Pipelined and Flash ADCs alternatives but do not meet the power efficiency requirements of mobile devices. Therefore, to overcome this challenge, there has been extensive researches to make use of the SAR ADC in other ADC architectures, often called "Hybrid" ADCs, which is an ADC architecture that fuses two different ADCs (e.g. Pipelined ADC and SAR ADC). By utilizing a Hybrid ADC architecture, designers can accomplish performances that were difficult with "Monolithic" ADCs.

#### 1.3.1 Pipelined-SAR ADCs

Here, we will study deeper on "Pipelined-SAR ADCs", which are one of the most successful Hybrid ADCs to date.

While we say "Pipelined ADCs are power-hungry", why is that? One of the major reasons is that Pipelined ADC requires *multiple* power-hungry Opamps (and amplification circuitry), depending on the number of Pipelined stages. Therefore, Pipelined-SAR ADC aims to lower the power consumption by minimizing the number of Pipeline stages by utilizing a SAR ADC as the high-resolution Quantizer [33] [34]. Conventionally, Flash ADCs were utilized as the Quantizer but its resolution was limited to 4-bit since the required number of comparators must increase exponentially with resolution. By replacing the Flash ADC to a SAR ADC, the quantizer resolution can be greatly improved over the limits (> 6-bits). While such configuration impacts the conversion speed, since SAR ADCs are much slower, this can be countered in deep scaled CMOS where the SAR ADC conversion speed improves.

32

The Pipelined-SAR ADC in [33] uses a two-stage configuration of 6-bit 1st stage SAR + 6-bit 2nd stage SAR to construct a 12-bit ADC in total. The residue voltage generated in the 1st stage SAR ADC is amplified  $64 \times$  and sampled via the 2nd stage SAR, realizing a two-stage operation. Since only one residue amplifier is required, the overhead of pipelining is minimized and high power efficiency can be obtained.

1.3

Moreover, Pipelined-SAR ADC holds several merits over the SAR ADC as well. Firstly, the conversion speed excels. Pipelined-SAR ADCs require only 6 SA cycles and amplification during the conversion cycle, in contrary to the 12-bit SAR ADC which requires 12 SA cycles. Besides, since the conversion is performed in twosteps, the reference voltage settling requirements are greatly relaxed. Specifically, if there is 0.5-bit redundancy between stages, the reference voltage requirement of each stage is only the 1/4 of the 6-bit LSB (which is equivalent to 16 LSB for full 12-bit resolution). Compared to 12-bit SAR ADCs which require the reference to settle within 1/4 of the 12-bit LSB, the design of reference buffers or decoupling capacitors is significantly relaxed, which will contribute to reducing the total system cost. Thus, the hybrid architecture combining pipeline and SAR ADCs can enjoy the advantages of both architectures and achieve both high performance and high power efficiency.

#### 1.3.2 Design challenges of the Pipelined-SAR ADC

However, even though Pipelined-SAR ADCs achieve high performance, significant design challenges remain.

1.) **Pipelined-SAR ADCs requires high precision residual amplification.** For such amplification, a high-gain opamp is indispensable but such designs are difficult to realize in scaled CMOS process. While various approaches have been taken to realize high-gain amplifiers in scaled CMOS (detailed benchmarks will be done in Chapter 2), none have been able to completely overcome the analog process scaling challenges.

2.) Most designs utilize complex digital gain calibrations. Hence, many

Figure 1.9: Thesis organization.

designs utilize digital calibration to counter the gain error and tolerate the use of a low-gain amplifier. Since precise gain is not required, this approach allows the use of power-efficient open-loop (or dynamic) amplifiers [30] [31]. However, sudden supply voltage variations cannot be tracked and suppressing such fluctuations with bypass capacitors significantly impacts chip cost. While environment variation tracking dynamic amplifiers have been proposed, start-up calibration is still necessary [35]. Such gain-calibrations are very complex, which typically takes several tens of ms and requires additional analog circuits as well. Such calibration overheads are further discussed in chapter 2.

To conclude, while Hybrid ADCs achieved a breakthrough in performance, it is not a silver bullet towards process scalability and several critical design challenges remain.

1.4

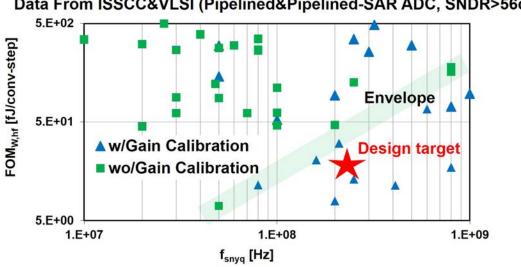

Data From ISSCC&VLSI (Pipelined&Pipelined-SAR ADC, SNDR>56dB)

Figure 1.10: Benchmark for high-speed high-resolution Pipelined ADCs.

#### 1.4 Thesis motivation and organization

In this thesis, design techniques towards CMOS process scalable and power-efficient Nyquist ADCs are explored. Our thesis construction is shown in Fig.1.9. The key approach we take upon realizing a process scalable ADC is: 1) aggressively utilize the scalable successive approximation (SA) circuitry and 2) propel a Hybrid with the existing ADC architectures.