## 学位論文 博士(工学)

マルチモード・マルチバンド対応の 無線通信用 RF 送信機の研究

2016年1月

慶応義塾大学大学院理工学研究科

中村 宝弘

## 本論文の構成と内容

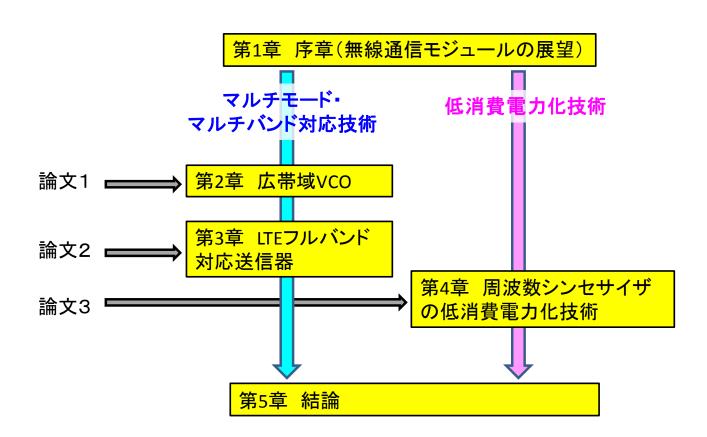

本研究は、複数の無線通信方式に対応可能な移動体端末向けの無線通信モジュール実現に向けたRFICの回路設計技術の開発を目的に、特にマルチモード・マルチバンド対応のために必要な技術と、消費電力削減のために必要な技術に関して検討したものである。前者については、移動体通信方式の一つであるLTE(Long Term Evolution)方式のフルバンド対応のために必要な技術を検討し、周波数シンセサイザの広帯域化と、部品点数削減に必須の送信信号の低雑音特性と高線形性の両立およびチップサイズ低減のための技術を提案し、試作・評価を通じてこれらの有効性を確認した。後者については、周波数シンセサイザの低消費電力化技術を検討し、低消費電力の電圧制御発振回路と、周波数分周回路を提案し、試作・評価を通じて有効性を確認した。

第1章は序論であり、本研究の対象であるモバイル端末の無線通信を取り巻く近年の状況 や必要とされる技術などの背景を述べる。

第2章では、LTE フルバンド対応に向けた電圧制御発振回路(VCO)の広帯域化と、それに伴う課題である周波数変換利得変動の抑圧技術の詳細について述べる。トランスフォーマ結合を介した周波数制御技術を導入した結果、試作した VCO では従来の 1/3 まで周波数変換利得変動を抑圧することに成功した。

第3章では、マルチモード・マルチバンド対応に伴い部品点数が増大することによって、無線通信モジュールが大型化してしまう問題に対して、弾性表面波(SAW)フィルタと差動単相変換素子(バラン)を削減可能な送信回路の技術の詳細を述べる。SAW フィルタ削減に不可欠な低雑音特性達成に向け、低雑音・高線形の直交変調器を導入し、十分な低雑音特性を達成した。また、バランを削減するために小型のチップ内蔵バランを導入し、従来のバランに比べてサイズを31%縮小できることを確認した。

第4章では、周波数シンセサイザの低消費電力化を目的に、周波数シンセサイザで最も消費電力の大きい2つの回路(VCOと周波数分周器)について、消費電力低減のための検討結果を述べる。2つのトランスフォーマによる出力を用いたVCOと、シングル・バランス・ミキサを用いたダイナミック周波数分周回路を提案した。VCOは消費電力11.1 mWで-109 dBc/Hz(1 MHz 離調時)の位相雑音特性を達成し、性能指標(FOM)による比較では従来よりも4dB高い性能となることを確認した。周波数分周器は、1.15 mW の低消費電力で、必要な周波数範囲での分周動作を確認した。

第5章は結論として、第1章から第4章までで得られた内容をまとめ、さらに今後の展望を述べる。

## 目次

| 第1章 序     | 論                                 | 4  |

|-----------|-----------------------------------|----|

| 1.1 はじめ   | 0{こ                               | 5  |

| 1.2 携帯電   | 話におけるマルチモード、マルチバンド対応の要求           | 8  |

| 1.3 移動体   | 端末用 RF モジュールの構成について               | 9  |

| 1.4 RFIC  | の構成について                           | 12 |

| 1.5 RF 通付 | 言モジュールのマルチモード、マルチバンド対応における課題      | 14 |

| 1.6 RFIC  | こおける課題                            | 15 |

| 1.7 本研究   | 色の目的                              | 15 |

| 1.8 本論文   | この構成について                          | 17 |

| 第 2 章 周   | 波数シンセサイザの GSM/ WCDMA/ LTE フルバンド対応 | 23 |

| 2.1 背景    |                                   | 24 |

|           | の設計                               |    |

|           | CO の広帯域化による課題と設計目標                |    |

| 2.2.2 VC  | CO のブロック構成                        | 30 |

|           | 振回路の設計                            |    |

| 2.2.4 VC  | CO の回路形式の検討                       | 32 |

|           | 性コンダクタンス生成回路の設計                   |    |

| 2.2.6 レ   | イアウト設計                            | 39 |

| 2.3 VCO   | D評価                               | 39 |

| 2.3.1 周   | 波数可変範囲と周波数変換利得                    | 40 |

| 2.3.2 位   | 相雜音特性                             | 42 |

| 2.3.3 性   | 能比較                               | 43 |

| 2.4 まとめ   | )                                 | 44 |

| 第3章 送     | 信回路                               | 46 |

| 3.1 背景    |                                   | 47 |

|           | 送信機の設計                            |    |

| 3.2.1 LT  | E 用送信機プロトタイプ                      | 50 |

| 3.2.2 QI  | MOD コア回路                          | 51 |

| 3.2.3 RI  | F-PGA の設計                         | 56 |

| 3.2.4 バ   | ランの設計                             | 57 |

| 3.3 LTE 用 | 送信機の測定結果                          | 62 |

| 3.4 まとめ   | )                                 | 74 |

| 第 4 章 周波数シンセサイザの低消費電力化技術 | 77  |

|--------------------------|-----|

| 4.1 背景                   | 78  |

| 4.2 回路設計                 | 79  |

| 4.2.1 VCO の設計            | 81  |

| 4.2.2 周波数分周器(DIV1)の設計    | 87  |

| 4.3 測定結果                 | 91  |

| 4.4 まとめ                  | 102 |

| 第 5 章 結論                 | 105 |

| 5.1 本研究のまとめ              | 106 |

| 5.2 今後の展望                | 107 |

| 謝辞                       | 108 |

| 著者論文目録                   | 109 |

# 第1章 序論

## 1.1 **はじめに**

無線通信は、空気を媒体として伝搬する電波を利用し、情報を送受信する通信である。黎明期には、1865年に英国で J. C. Maxwell がマクスウェル方程式を解いて電波の存在を予言する [1] など、欧州を中心に技術開発が進むが、商用化されて広く普及した代表格は、米国で開発されたラジオやテレビなどの放送と、携帯電話などの移動体通信、および無線 LANである。

アナログ放送に関しては、米国で、1920年に AM(Amplitude Modulation)ラジオ放送が、1938年には AM ラジオ放送よりも雑音に強い FM(Frequency Modulation)ラジオ放送が開始された。さらに、音声だけでなく映像も送信する白黒テレビ放送(1937年)、カラーテレビ放送(1958年)、静止衛星を用いたアナログ衛星放送(1988年)へと発展した。その後、直交周波数多重分割(OFDM: Orthogonal Frequency Division Multiplexing)方式 [2-7] のデジタル変調とデジタル圧縮技術により通信データ量を大幅に拡大したことで高解像の映像を送信できるデジタルテレビ放送(2000年に衛星放送、2003年に地上波放送)が開始され、現在に至っている。

移動体通信に関しては、表 1-1 に示すように、1979 年に日本で最初の携帯電話としてアナログ変調方式の携帯電話サービスが開始され、主に自動車電話として普及した。その後小型化が進み、第 1 世代携帯電話として普及していった。1993 年に第 2 世代のデジタル通信方式 (GSM: Global System for Mobile Communications) [8] が開始されると、携帯電話は爆発的に普及した。この頃から、携帯電話は単に通話を行うための機器ではなく、メールなどのパケット通信が行える機能を標準で備えるようになる。さらに携帯電話がインターネットへの接続機能も備えるようになると、その通信容量の拡大が求められるようになった。

通信容量拡大の要求に伴って、2000 年頃に GSM 方式の変調方式を 8PSK に拡張した第 2.5 世代の通信方式 (EDGE: Enhanced Data Rates for GSM Evolution) [8]によって、最大 473.6 kbps のデータ通信が、続いて 2001 年には最大 5 MHz の帯域を使用する第 3 世代の通信方式 (WCDMA: Wideband Code Division Multiple Access) [9] により最大 2 Mbps のデータ通信が 行えるサービスが始まった。2005 年には、WCDMA のパケット通信規格と変調方式を QPSK (Quadrature Phase Shift Keying) から 16QAM (Quadrature Amplitude Modulation) へ拡張した第 3.5 世代の通信方式 (HSPA: High Speed Packet Access) [9] により最大 14 Mbps の、2010 年には OFDM の 2 次変調方式と MIMO (Multi-Input Multi-Output) [10-12] の空間多重技術 を活用した第 3.9 世代の通信方式 (LTE: Long Term Evolution) [13] により最大 100 Mbps のデータ通信が行えるようになるなど、順調に通信容量は拡大している。2014 年にはキャリア・アグリゲーション (CA: Carrier Aggregation) 技術を採用した第 4 世代の通信方式 (LTE-A: LTE Advanced) [13] を用いたサービスが開始され、将来的には最大 3 Gbps (下り、上りは 1.5 Gbps) のデータ通信を行えるようになる予定である。

表 1-1 携帯電話方式の世代ごとの特徴

| 世代       | サービス<br>開始年 | 携帯電話<br>方式   | 最大<br>帯域幅    | 変調方式                   | 最大通信レート<br>(上り/下り)      | 特徴技術         |

|----------|-------------|--------------|--------------|------------------------|-------------------------|--------------|

| 第1世代     | 1979年       | AMPS<br>TACS | 30kHz        | FM/FSK                 | -                       | アナログ<br>変調   |

| 第2世代     | 1993年       | GSM<br>PDC   | 400kHz       | GMSK<br>GPRS           | 171.2kbps<br>/171.2kbps | デジタル<br>変調   |

| 第 2.5 世代 | 2000 年頃     | EDGE         | 400kHz       | 8PSK                   | 473.6kbps<br>/473.6kbps |              |

| 第3世代     | 2001年       | WCDMA        | 5MHz         | QPSK                   | 2Mbps<br>/2Mbps         | CDMA         |

| 第 3.5 世代 | 2005年       | HSPA         | 5MHz         | QPSK<br>16QAM          | 11.5Mbps<br>/14.4Mbps   |              |

| 第 3.9 世代 | 2010年       | LTE          | 20MHz        | QPSK<br>16QAM<br>64QAM | 50Mbps<br>/100Mbps      | OFDM<br>MIMO |

| 第4世代     | 2014 年      | LTE-A        | 100MHz<br>×2 | QPSK<br>16QAM<br>64QAM | 1.5Gbps / 3Gbps         | CA           |

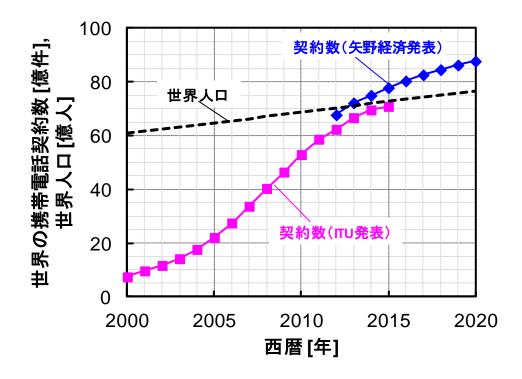

図 1-1 世界の携帯電話契約件数と世界人口の推移

図 1-1 は、世界の携帯電話契約件数と世界人口の推移である。契約件数は年々増加しており、国際電気通信連合(ITU: International Telecommunication Union)の発表によれば、2015年には世界人口にほぼ等しくなることが推測されている。さらに、矢野経済研究所の発表によれば、2015年以降も世界の携帯電話契約件数は増加し続け、2020年には世界人口の 1.1倍の 88億件に達することが予測されている。

表 1-2 に示すように、無線 LAN 通信の規格は、1999 年に 2.4 GHz 周辺の ISM(Industry Science Medical)帯を用いた IEEE802.11b(最大 11Mbps)と、5GHz 帯で OFDM 変調を用いた IEEE802.11a (最大 54 Mbps) が策定された。無線 LAN でも通信容量拡大の要求は大きく、2003 年には 2.4GHz 帯で OFDM 変調を用いた IEEE802.11g(最大 54 Mbps)が、2009 年には 2.4GHz や 5GHz 帯で 64QAM の変調方式と MIMO(Multi-Input Multi-Output)の空間多重技術を用いた IEEE802.11n(最大 600 Mbps)が、2014 年には 5GHz 帯で 256QAM の変調方式を用い、さらにチャネル帯域と空間多重を増大した IEEE802.11ac(最大 6.9Gbps)が策定された。2013 年には、近距離の通信を行う 60 GHz 帯を用いた規格である IEEE802.11ad(最大 6.8 Gbps)も策定され、2020 年頃を目標に開発が進められている 5G 通信では、移動体通信と IEEE802.11ad 通信を協調して動作させるアシスト機能も提案されている。

表 1-2 無線 LAN の規格ごとの特徴

| 規格           | 策定年    | 周波数帯               | 最大<br>帯域幅 | 変調方式                               | 最大通信レート<br>(上り/下り)   | 特徴技術 |

|--------------|--------|--------------------|-----------|------------------------------------|----------------------|------|

| IEEE802.11b  | 1999 年 | 2.4GHz 帯           | 22MHz     | DBPSK<br>DQPSK<br>CCK              | 11Mbps /22Mbps       |      |

| IEEE802.11a  | 1999 年 | 5GHz 帯             | 20MHz     | BPSK<br>QPSK<br>16QAM              | 54Mbps<br>/54Mbps    | OFDM |

| IEEE802.11g  | 2003年  | 2.4GHz 帯           | 20MHz     | (D)BPSK<br>(D)QPSK<br>CCK<br>16QAM | 54Mbps<br>/54Mbps    |      |

| IEEE802.11n  | 2009年  | 2.4GHz 带<br>5GHz 帯 | 40MHz     | BPSK<br>QPSK<br>16QAM<br>64QAM     | 600Mbps<br>/600Mbps  | MIMO |

| IEEE802.11ac | 2014 年 | 5GHz 帯             | 160MHz    | 64QAM<br>256QAM                    | 6.9Gbps<br>/ 6.9Gbps |      |

| IEEE802.11ad | 2013年  | 60GHz 帯            | 9GHz      | 16QAM<br>64QAM                     | 6.8Gbps<br>/6.8Gbps  | ミリ波  |

## 1.2 携帯電話におけるマルチモード、マルチバンド対応の要求

スマートホンやタブレット端末に代表されるモバイル端末の普及に伴い、動画像や音楽などの大容量データを素早く、簡便にやりとりすることが強く求められている。この要求に伴って、1-1 節で示したように、移動体通信を利用した通信容量の拡大が進められている。日本においては LTE 通信に注目が集まりインフラも全国に整備されつつあるが、通信方式の導入状況と計画は各々の国・地域で異なり、欧州の先進国でも依然として GSM 方式とWCDMA 方式が広く使われている。さらに、GSM、WCDMA、LTE で用いる周波数バンドには、表 1-3 に示すように複数のバンドが設定されており、国・地域や通信キャリアによって使用するバンドが異なる。このような情勢から、高速通信を行うモバイル端末は、GSM/EDGE/WCDMA/HSPA/LTE/LTE-A 方式全てに対応することと、主要な周波数バンド全てに対応することが求められている[14-26]。

表 1-3 移動体通信用バンド

|         | 周波数 (MHz) |        |        |        |        |

|---------|-----------|--------|--------|--------|--------|

| Band    | 上り        |        | 下り     |        | 国、地域   |

|         | Min.      | Max.   | Min.   | Max.   |        |

| GSM850  | 824       | 849    | 869    | 894    | 北米     |

| GSM900  | 890       | 915    | 935    |        | グローバル  |

| DCS1800 | 1710      | 1785   | 1805   | 1880   | グローバル  |

| PCS1900 | 1850      | 1910   | 1930   | 1990   | 北米     |

| Band1   | 1920      | 1980   | 2110   | 2170   | 日、中、欧  |

| Band2   | 1850      | 1910   | 1930   | 1990   | 北米     |

| Band3   | 1710      | 1785   | 1805   | 1880   | グローバル  |

| Band4   | 1710      | 1755   | 2110   | 2155   | 北米     |

| Band5   | 824       | 849    | 869    | 894    | 北米     |

| Band7   | 2500      | 2570   | 2620   | 2690   | 北米、欧、中 |

| Band8   | 880       | 915    | 925    | 960    | 日、欧    |

| Band11  | 1427.9    | 1447.9 | 1475.9 | 1495.9 | 日      |

| Band12  | 699       | 716    | 729    | 746    | 北米     |

| Band13  | 777       | 787    | 746    | 756    | 北米     |

| Band14  | 788       | 798    | 758    | 768    | 北米     |

| Band17  | 704       | 716    | 734    | 746    | 北米     |

| Band18  | 815       | 830    | 860    | 875    | 日      |

| Band19  | 830       | 845    | 875    | 890    | 日      |

| Band20  | 832       | 862    | 791    | 821    | 欧      |

| Band21  | 1447.9    | 1462.9 | 1495.9 | 1510.9 | 日      |

| Band23  | 2000      | 2020   | 2180   | 2200   | 北米     |

| Band24  | 1626.5    | 1660.5 | 1525   | 1559   | 北米     |

| Band25  | 1850      | 1915   | 1930   | 1995   | 北米     |

| Band26  | 814       | 849    | 859    | 894    | 日      |

| Band28  | 703       | 748    | 758    | 803    | 日      |

| Band30  | 2305      | 2315   | 2350   | 2360   | 北米     |

| Band38  | 2570      | 2620   | 2570   | 2620   | 欧、中    |

| Band39  | 1880      | 1920   | 1880   | 1920   | 中      |

| Band40  | 2300      | 2400   | 2300   | 2400   | 中      |

| Band41  | 2496      | 2690   | 2496   | 2690   | 北米、中   |

| Band42  | 3400      | 3600   | 3400   | 3600   | 日      |

さらに、近年のモバイル端末には、移動体通信だけでなく数十メートル程度の中距離で通信を行う無線 LAN 通信機能も標準的に搭載されている。無線 LAN の搭載によって、ユーザは周辺の無線環境に合わせて通信方式を切り替えて使用することができ、通信コストを抑えたり、より快適な通信方式を選択したりすることを可能にしている。無線 LAN の環境は設置する業者や個人によって異なるため、携帯電話は IEEE802.11a/b/g/n/ac 全てに加えて、将来的には 60 GHz のミリ波(30 GHz~300 GHz)帯を用いる IEEE802.11ad への対応も求められていくことが予測されている。

このようにモバイル端末の通信機能は拡充の一途を辿り、以上の通信機能全てに加えて、 全地球測位システム (GPS: Global Positioning System) や近距離無線通信システム (Bluetooth など) などの無線通信機能も搭載されている。

## 1.3 移動体端末用 RF モジュールの構成について

1-2 節で述べたように、モバイル端末には多くの通信機能が搭載される。その中でも特にモジュールのサイズが大きく使用頻度の高い移動体通信の RF モジュールの構成について考える。移動体通信用 RF モジュールの構成を考える上でキーとなる重要な仕様は、(全ての仕様が重要ではあるが、)最小受信感度、ブロッキング特性、表 1-3 に示した対応バンドである。最小受信感度は、端末が信号を受信して復調できる最小の受信電力であり、例えばLTE Band1 における 20 MHz 帯域のシステムでは、-93.3 dBm 以下である必要がある [13]。 熱雑音  $P_{n,th}$  は以下の式

$$P_{n_{-}th} = k_B T \Delta f \tag{1-1}$$

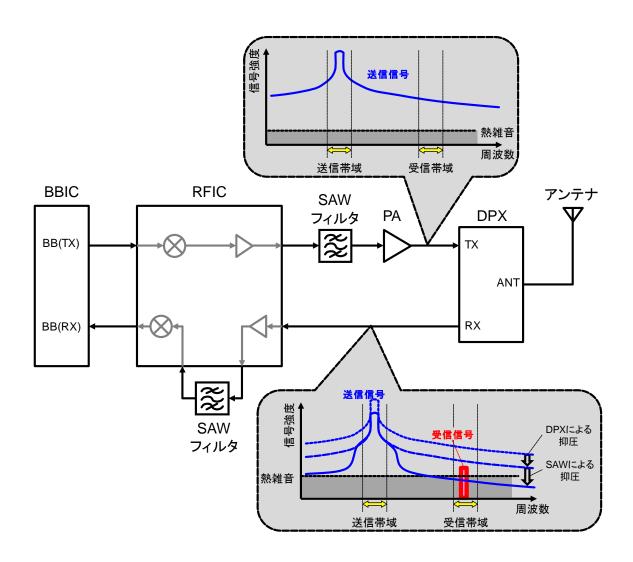

で表される。ここで $k_B$ 、T、 $\Delta f$ は、それぞれボルツマン定数、絶対温度、信号の周波数帯域である。85℃の時の 20 MHz 帯域内の熱雑音は、-100.1 dBm である。すなわち、上記の最小受信感度は、熱雑音に対して 6.8 dB だけ大きい信号まで受信して復調できる必要があることを示している。これを実現するには、RF モジュールの雑音指数を低くするだけでは十分でなく、他の雑音も考慮する必要があり、それにはモジュールの構成が重要になる。は、LTE バンド1 用の RF モジュールの構成例である。移動体端末では送受でアンテナを共用するが、LTE は送受が同時に動作する周波数分割方式であるため、送信と受信を分離するためにデュプレクサ(DPX)と呼ばれる分波器を備える。理想的な DPX の特性は、送信周波数においては送信端からアンテナへの損失がゼロで、かつアンテナから受信端へ信号が漏えいしないこと、受信周波数においてはアンテナから受信端の損失がゼロで、かつ送信端からアンテナへ信号が漏えいしないことであるが、実際には理想的にはならず、に示すように受信周波数において送信端からアンテナへわずかながら信号が漏えいし、これが受信端にも漏えいする。

DPX の種類や大きさによって漏えい量は異なるが、一般的な DPX [27] では受信周波数における送信端から受信端への漏えい量は-45dB 程度である。送信信号のスペクトルは理想的には送信周波数帯域内に収まるが、実際には位相雑音によって裾野が広がる。 DPX に漏えいがあるため、送信信号の位相雑音成分が受信端に回り込んで受信感度が悪化する問題が発生する。最小受信電力、受信帯域における単位周波数あたりの送信雑音 (@DPX の TX 端子)、 DPX の送受間アイソレーション、受信雑音指数、必要なリンクマージンを、それぞれ  $P_{RX}$ 、 $P_{RX}$ 、 $P_{RX}$ 、 $P_{RX}$ 、 $P_{RX}$ 、 $P_{RX}$  とすると、以下の不等式を満たさなければならない。

$$P_{RX} / M \cdot \Delta f \ge F_{RX} \cdot k_B T + p_{n_{-}TX} \cdot I_{TRX}$$

(1-2)

図 1-2 LTE バンド 1 用の RF モジュールの構成例

例えば、DPX の送受間アイソレーションが-45 dB、雑音指数が 2 dB、リンクマージンが 3 dB とすると、単位周波数あたりの送信雑音は DPX の入力において-131.7 dBm/Hz 以下(送信電力は 25 dBm が最大であるため-156.7 dBc/Hz 以下)と非常に小さくしなければならない。この問題への対策として、従来は送信信号をフィルタ(表面弾性波(SAW: Surface Acoustic Wave)フィルタが主流)を介して出力する構成としていた。SAW フィルタの損失が問題となるため、パワーアンプの前段にフィルタを用いるのが一般的である。

ちなみに GSM 方式では、受信帯域における送信雑音が送信エミッションマスクとして 3GPP [8] で明確に仕様化されており、例えば 850 MHz 帯を用いる GSM850 では、-79 dBm/100 kHz 以下(送信電力が+33 dBm であるため-162 dBc/Hz 以下)の受信帯域雑音を実現する必要がある。

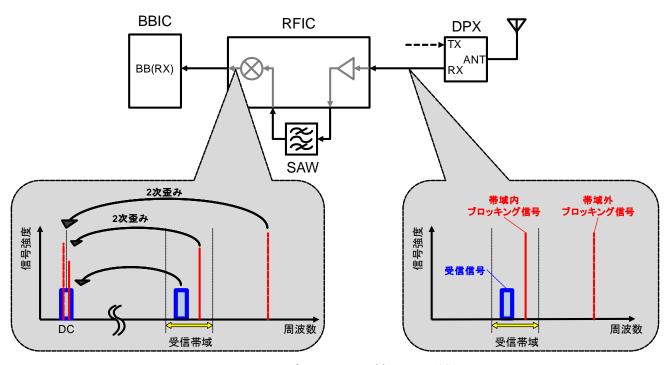

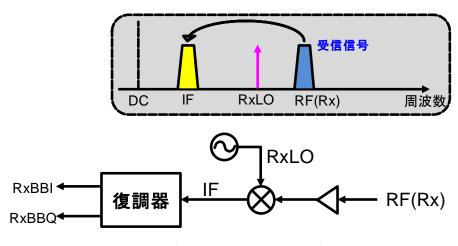

図 1-3 ブロッキング信号の影響

ブロッキング特性は、多くの無線通信信号が飛び交う現在の電波状況においては、非常に重要な特性である。ブロッキング特性には、帯域内の干渉波に対するブロッキング特性([13]のセクション 7.6.1)と、帯域外の干渉波に対するブロッキング特性([13]のセクション 7.6.2)に分けられる。図 1-3に示すように、帯域内・帯域外に関わらず、ブロッキング信号は、受信ミキサによって自身の 2次変調成分が DC 近傍にダウンコンバージョンされる [28] ため、ダイレクト・コンバージョン形式の場合には所望波と同じ周波数に現れ、SN 比が劣化する。この問題への対策は 2次歪み特性を良好にすることであり、補正技術 [29-32] が広く使われ

ている。また、ブロッキング信号の大きさに比例して問題が大きくなるため、帯域内に比べて信号強度の大きい帯域外ブロッキング信号でより顕著に問題になる。従来は、受信信号にフィルタ(SAW フィルタが主流)をかけて帯域外のブロッキング信号を抑圧して受信する構成としていた。送信の場合と同様に、SAW フィルタの損失による雑音指数の悪化が問題となるため、初段の低雑音増幅器の後段にフィルタを用いるのが一般的である。

以上に示したようなRFIC、SAW フィルタ、パワーアンプ、デュプレクサを用いて構成されるのが従来の移動体端末用RFモジュールであるが、対応するバンドが増えるにしたがって、構成部品が増大し、モジュールサイズが大きくなる課題がある。

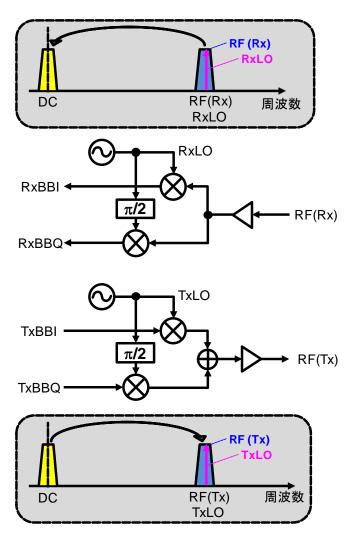

## 1.4 RFIC の構成について

RFIC の構成は、雑音やブロッキング特性を考慮して決定されている。受信器の構成につ いては、搬送波周波数 (Radio Frequency) と局部発振 (Local Oscillator) 信号周波数が等し いダイレクト・コンバージョン形式(図 1-4)を用いた場合には、一般的に DC オフセット やブロッキング信号の 2 次変調が問題になる [33] ため、DC オフセットと 2 次歪みを補正 する機構が必要不可欠である。しかしながら、バイポーラ・トランジスタ・プロセスで RFIC を作製していた 1990 年代には、DC オフセット補正や 2 次歪み補正を実施するための論理 回路やスイッチ回路の内蔵が困難であったため、単一中間周波数 (Intermediate Frequency) 形式[34-36]やデュアル IF 形式[37] のように、RF が LO 周波数と異なり、ダウンコンバート 信号が DC を含まないヘテロダイン形式(図 1-5)を用いることが主流であった。ところが ヘテロダイン形式は外付けの IF 帯フィルタを必要とするため、小型化・低コスト化の要求 から外付け IF 帯フィルタが不要なダイレクト・コンバージョン形式への移行が求められる ようになった。1990年代後半に、バイポーラ・プロセスに CMOS トランジスタも搭載する BiCMOS プロセスが登場したことによって、DC オフセット補正技術 [38-40] や 2 次歪み補 正技術 [29-32] を採用することが可能となったことで、ダイレクト・コンバージョン形式が 広く用いられるようになった。2015年現在は、65nm CMOS や45nm CMOS プロセスによっ て作製されたダイレクト・コンバージョン形式が主流となっている。

また、LTE 以降の移動体通信では、MIMO 技術を用いるため、受信回路は複数のパスを持つ必要がある。現在は、メインの信号経路以外に、ダイバーシティ信号経路を備えるトランシーバが報告されている [41,42]。

送信の構成については、GSMでは1-3節で述べたように出力雑音の仕様が厳しいことと、変調方式が位相変調のみで振幅変調を必要としないことから、ミキサを用いずに電圧制御発振器に直接変調をかけるポーラ・ループ形式 [37,43-46] やオープン・ポーラ形式 [47] が主に用いられてきた。第2.5世代以降は振幅変調も必要になるため、図1-4に示すようなダイ

レクト・コンバージョン形式が主流であるが、オープン・ポーラ形式と振幅変調器を併用する構成 [47] も用いられている。第3世代以降はダイレクト・コンバージョン形式が主流であるが、GSM との回路共通化によってチップ面積を低減する目的で、GSM でもダイレクト・コンバージョン形式が用いられる動き [42] や、逆に WCDMA や LTE をポーラ形式で実現する構成 [48,49] も提案されている。前者は受信帯域雑音特性の達成が課題であり、後者は位相変調信号と振幅変調信号間のレイテンシ差による EVM (Error Vector Magnitude) などの信号品質劣化が課題である。

図 1-4 ダイレクト・コンバージョン形式受信受信器と送信機のブロック構成図

図 1-5 ヘテロダイン形式受信器のブロック構成図

## 1.5 RF 通信モジュールのマルチモード、マルチバンド対応における課題

1-2 節で述べた理由から、移動体通信用の RF モジュールは、複数の通信方式と複数のバンドに対応できることが求められている。第 2 世代の初期の頃は、GSM の中でも GSM900 のみに対応した IC がトランシーバとして開発され、その後 GSM850 と GSM900 のデュアルバンド対応トランシーバや、PCS と DCS まで含めたクアッドバンド対応のトランシーバが開発された。これらのマルチバンド対応を可能にしたのは、BiCMOS プロセスや CMOS プロセスによってアナログ回路のデジタル制御が可能になったことや、フラクショナル PLL、広帯域で低消費電力の電圧制御発振回路や低雑音増幅回路などのアナログ回路技術の発展が寄与している。さらに、GSM/EDGE/WCDMA のマルチモード対応なども実現され、加えてLTEの複数バンド対応も可能となっているが、2015 年現在では対応可能なバンドは表 1-3の一部に限られている。理想的には表 1-3の全バンドに対応可能であることが求められるが、そのためには上述のアナログ回路の広帯域化技術や低消費電力化技術をさらに進めることや、以下に示す部品点数削減のための技術に取り組まなければならない。

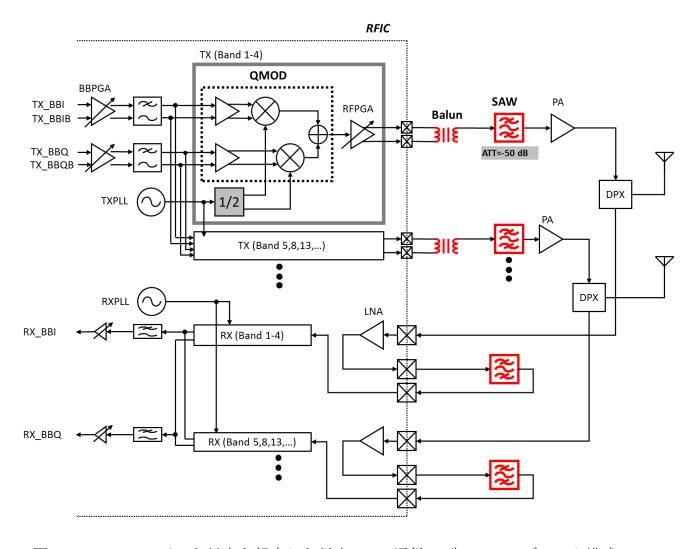

全バンド対応の要求は高いものの、対応バンド数の増大に伴って部品点数も増大することから、RF通信モジュールのサイズが大きくなる課題が発生している。図 1-6 に、LTE フルバンド対応を想定した RF 通信モジュールのブロック構成を示す。1-3 節で述べたように、従来は送信・受信ともに SAW フィルタを備えるが、バンド数の増大によって SAW フィルタと差動単相変換器(バラン(BALUN: Balance to Unbalance))の個数も増大する。さらには受信のダイバーシティ経路にも SAW フィルタが必要となる。このような経緯によって、SAW フィルタやバランを削除する要求が高まっている。SAW フィルタを削除するには、受

信においてはブロッキング信号への耐性を強くすること、送信においては送信雑音を低減することが必要になる。バラン部品を削除するには、バランを RFIC に内蔵する必要がある。

## 1.6 **RFIC** における課題

全バンド対応時の RF 通信モジュール小型化の要求に対して、受信回路においては、25% デューティの局部発振 (LO) 信号を用いることで周波数選択性を高めたり[50]、2 次変調の問題を補正する回路を用いたり [29-32] することで、受信用 SAW フィルタの削減を可能にして小型化が進められている。

送信回路においては、SAW フィルタ削除による小型化に向けた低雑音化のため、25%デューティの局部発振(LO)信号を用いた受動ミキサ [15-17] や、ミキサとドライバアンプを共通化したいわゆるパワーミキサ[51]、または周波数が LO の 2 倍の信号を用いてサンプリングすることで分周器の雑音をマスクできるミキサ回路[8]などを用いることで、送信信号の雑音を低減することに成功している。低雑音化が可能となったことで複数の LTE バンドに対応する SAW フィルタレスの送信機が実現されているものの、対応バンドは限定されている。これは、フルバンド対応を実現するには、RFIC の回路が増えることでチップサイズや消費電力が増大してしまい、コストと消費電力が要求に見合わなくなるためと考えられる。

また、バラン内蔵による小型化に向けては、マーチャンド・バランを用いた構成[18]や、トランスフォーマ・バランを用いた構成[51]が報告されているが、損失を抑えるためにサイズが大きくなる問題がある。

以上のように、小型のLTE フルバンド対応 RF 通信モジュールを実現するには、RFIC のチップサイズと消費電力が増大する課題に取り組む必要があり、小面積のフルバンド対応周波数シンセサイザをや、それに対応できる送信回路の実現、およびバランの小型化などによるチップサイズ低減と消費電力の低減が不可欠となる。

## 1.7 本研究の目的

本研究では、上で述べたLTEフルバンド対応に必要なRFICの技術開発を目的としている。 フルバンド対応時に課題となるチップサイズ低減に向けて、周波数シンセサイザ用の広帯域 電圧制御発振回路(VCO: Voltage controlled oscillator)について検討した。また、SAW フィルタとバラン部品を削除してモジュールサイズを低減するために必要となる、低消費電力で の送信雑音低減と小面積でのオンチップ・バランの実現に向けて、送信回路について検討した。さらに、消費電力低減に向けて、周波数シンセサイザで消費電力の大きい VCO と周波数分周器の低消費電力化技術について検討した。この検討は、ISM (Industry-Science-Medical) バンドである 24 GHz 帯での無線通信システムの実現に向けて行ったものであるが、検討した技術は 24 GHz 特有のものではなく、移動体通信で用いるマイクロ波帯にも適用することが可能である。

図 1-6 LTE フルバンド対応を想定した従来の RF 通信モジュールのブロック構成

## 1.8 本論文の構成について

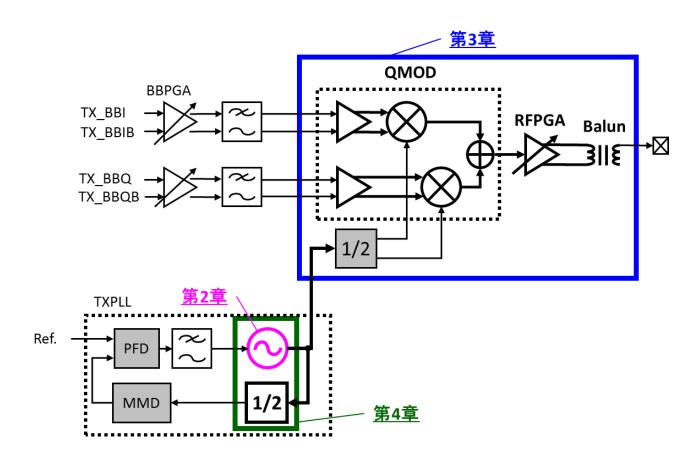

図 1-7 および図 1-8 に、本論文の構成を示す。第 1 章にて、対象である無線通信用 RFIC の研究背景と、マルチモード、マルチバンド対応および低消費電力化の課題について整理した。第 2 章は、フルバンド対応時に課題となるチップサイズ低減に向けて、周波数シンセサイザ用の VCO について提案した内容を述べる。第 3 章では、SAW フィルタとバラン部品を削除してモジュールサイズを低減するために必要となる、低消費電力での送信雑音低減と小面積でのオンチップ・バランの実現に向けて、提案した内容を述べる。第 4 章では、周波数シンセサイザ、特に電圧制御発振回路と周波数分周回路の低消費電力化技術について述べる。第 5 章では、第 2 章から第 4 章で述べた技術を組み合わせることで実現されることが期待される移動体通信用 RFIC について述べるとともに、結論を述べる。

図 1-7 本論文の構成

図 1-8 本論文の構成(送信回路のブロックで説明)

## 参考文献

- [1] J. C. Maxwell, "A Dynamical Theory of the Electromagnetic Field", *Phil.Trans.Roy.Soc.Lond.* 155, pp.459–512, 1865.

- [2] R.W. Chang, "Synthesis of band-limited orthogonal signals for multichannel data transmission," *BSTJ*, Vol.45, pp.1775-1796, 1966.

- [3] R.W. Chang, and R.A. Gibby, "A theoretical study of performance of an orthogonal multiplexing data transmission scheme," *IEEE Trans. Comm.*, Vol. 16, No. 4, pp.529-540, 1968.

- [4] "Orthogonal frequency division multiplexing," US Patent 3,488,445, filed Nov. 14, 1966, issued Jan. 6, 1970.

- [5] S.B. Weinstein, and P.M. Ebert, "Data transmission by frequency-division multiplexing using the discrete Fourier transform," *IEEE Trans. Comm.*, Vol. 19, No. 5, pp.628-634, 1971.

- [6] B. Hirosaki, "An analysis of automatic equalizers for orthogonally multiplexed QAM systems," *IEEE Trans. Comm.*, Vol. 28, No. 1, pp.73-83, 1980.

- [7] L.J. Cimini, Jr, "Analysis and simulation of a digital mobile channel using orthogonal frequency division multiplexing," *IEEE Trans. Comm.*, Vol. 33, No. 7, pp.665-675, 1985.

- [8] Technical Specification Group GSM/EDGE Radio Access Network. 3rd Generation Partnership Project, Release 5 (2001-8).

- [9] 3GPP TS 25.101, "User Equipment (UE) radio transmission and reception (FDD)."

- [10] S. Verdu, Multiuser Detection. Cambridge, U.K.: Cambridge Univ. Press, 1998.

- [11] H. Liu, Signal Processing Applications in CDMA Communications. Norwell, MA: Artech House, 2000.

- [12] A.Burg, et al., "VLSI imprementation of MIMO detection using sphere decoding algorithm," *IEEE Journal of Solid-State Circuits*, vol. 40, pp.1566-1577, July 2005.

- [13] 3GPP, 3rd-Generation Partnership Project; Technical Specification Group Radio Access Network; LTE; Evolved Universal Terrestrial Radio Access (E-UTRA); User Equipment (UE) radio transmission and reception (Release 11), 3GPP TS 36.101 V11.5.0, Jul. 2013.

- [14] K. Ueda, T. Uozumi, R. Endo, T. Nakamura, T. Heima, and H. Sato, "A Digital PLL with Two-step Closed-locking for Multi-mode/Multi-band SAW-less Transmitter," in *Proc. of IEEE Custom Integrated Circuits Conf.*, September, 2012, pp. 1-4.

- [15] M. Farazian, B. Asuri, and L. E. Larson, "A Dual-Band CMOS CDMA Transmitter Without External SAW Filtering," *IEEE Trans. Microwave Theory and Techniques*, vol. 58, no. 5, pp. 1349-1358, May, 2010.

- [16] T. Sowlati, *et al.*, "Single-Chip Multiband WCDMA/HSDPA/HSUPA/EGPRS Transceiver with Diversity Receiver and 3G DigRF Interface Without SAW Filters in Transmitter / 3G Receiver Paths," in *IEEE Int. Solid-State Circuits Conf. Dig.*, Feb. 2009, pp. 116-117.

- [17] J. Craninckx, J. Borremans, and M. Ingels, "SAW-less Software-Defined Radio Transceivers in 40nm CMOS," in *Proc. of IEEE Custom Integrated Circuits Conf.*, September, 2011, pp. 1-8.

- [18] T. Kihara, T. Sano, M. Mizokami, Y. Furuta, T. Nakamura, M. Hokazono, T. Maruyama, K. Toyota, K. Maeda, Y. Akamine, T. Yamawaki, T. Heima, K. Hori, and H. Sato "A Multiband LTE SAW-Less CMOS Transmitter with Source-Follower-Driven Passive Mixers, Envelope-Tracked RF-PGAs, and Marchand Baluns", in *IEEE Radio Frequency Integrated Circuits Symp. Dig.*, pp. 399-402, June 2012.

- [19] S. D'Souza, F. Chang, S. Pamarti, B. Agarwal, H. Zarei, T. Sowlati, and R. Berenguer, "A Progammable Baseband Anti-Alias Filter for a Passive-Mixer-Based, SAW-less, Multi-Band, Multi-Mode WEDGE Transmitter," in *IEEE Int. Symp. on Circuits and Systems Dig.*, May 2011, pp.450-453.

- [20] X. He and J. van Sinderen, "A Low-Power, Low-EVM, SAW-Less WCDMA Transmitter Using Direct Quadrature Voltage Modulation," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3448-3458, December 2009.

- [21] V. Giannini, M. Ingels, T. Sano, B. Debaillie, J. Borremans, and J. Craninckx, "A Multiband LTE SAW-less Modulator with -160dBc/Hz RX-Band Noise in 40nm LP CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig.*, Feb. 2011, pp. 374-375.

- [22] M. Ingels, Y. Furuta, X. Zhang, S. Cha, and J. Craninckx, "A Multiband 40nm CMOS LTE SAW-Less Modulator with -60dBc C-IM3," in *IEEE Int. Solid-State Circuits Conf. Dig.*, Feb. 2013, pp. 338-339.

- [23] A. Cicalini, et al., "A 65nm CMOS SoC with Embedded HSDPA/EDGE Transceiver, Digital Baseband and Multimedia Processor," in *IEEE ISSCC Digest*, pp.368-369, 2011.

- [24] M. Nilsson, et al., "A 9-Band WCDMA/EDGE Transceiver Supporting HSPA Evolution," in *IEEE Int. Solid-State Circuits Conf. Dig.*, pp.366-367, 2011.

- [25] I. Liu, et al., "A SAW-less GSM/GPRS/EDGE Receiver Embedded in a 65nm CMOS SoC," in *IEEE Int. Solid-State Circuits Conf. Dig.*, pp.364-365, 2011.

- [26] F. Beffa, et al., "A Receiver for WCDMA/EDGE Mobile Phones with Inductor-less Front-End in 65nm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig.*, pp.370-371, 2011.

- [27] H. Nakamura, et al., "Development of Minature Surface Acoustic Wave Duplexer for Wide-band Code-Division Multiple-Access System," in *Panasonic Technical Journal*, Vol. 55, No. 2, pp.43-48, 2009.

- [28] D. Manstretta, et al., "Second-Order Intermodulation Mechanisms in CMOS Downconverters," *IEEE J. Solid-State Circuits*, vol. 38, no. 3, pp. 394-396, March 2003.

- [29] D. Kaczman, M. Shah, M. Alam, M. Rachedine, D. Cashen, L. Han, A. Raghavan, "A Single-Chip 10-Band WCDMA/HSDPA 4-Band GSM/EDGE SAW-less CMOS Receiver

- With DigRF 3G Interface and +90 dBm IIP2, "IEEE J. Solid-State Circuits, vol. 44, no. 3, pp. 718-739, Mach 2009.

- [30] M. Brandolini, P. Rossi, D. Sanzogni, and F. Svelto, "A +78 dBm IIP2 CMOS Direct Downconversion Mixer for Fully Integrated UMTS Receivers," *IEEE J. Solid-State Circuits*, vol. 41, no. 3, pp. 552-556, Mach 2006.

- [31] R. Bagheri, et al., "An 800-MHz–6-GHz Software-Defined Wireless Receiver in 90-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 41, no. 12, pp. 2860-2876, Dec. 2006.

- [32] S. Zhou, and M. F. Chang, "A CMOS Passive Mixer With Low Flicker Noise for Low-Power Direct-Conversion Receiver," *IEEE J. Solid-State Circuits*, vol. 40, no. 5, pp. 1084-1093, May 2005.

- [33] B. Razavi, "Design Considerations for Direct-Conversion Receivers," *IEEE Trans. Circuits & Systems—II*, Vol. 44, No. 6, pp. 428-435, June 1997.

- [34] T. Stetzle, et al., "A 2.7V to 4.5V Single-Chip GSM Transceiver RF Integrated Circuit," in *IEEE Int. Solid-State Circuits Conf. Dig.*, pp.150-151, 1995.

- [35] Q. Huang, et al., "GSM Transceiver Front-End Circuits in 0.25-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 34, no. 3, pp. 292-303, March 1999.

- [36] P. Orsatti, et al., "A 20mA-Receive 55mA-Transmit GSM Transceiver in 0.25μm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig.*, pp.232-233, 1999.

- [37] T. Yamawaki, et al., "A 2.7-V GSM RF Transceiver IC," *IEEE J. Solid-State Circuits*, vol. 32, no. 12, pp. 2089-2096, December 1997.

- [38] A. A. Abidi, "Direct-Conversion Radio Transceivers for Digital Communications," *IEEE Solid-State Circuits*, Vol. 30, No. 12, pp. 1399-1410, December 1995.

- [39] B. Bakkaloglu, et al., "A 1.5-V Multi-Mode Quad-Band RF Receiver for GSM/EDGE/CDMA2K in 90-nm Digital CMOS Process," *IEEE Solid-State Circuits*, Vol. 41, No. 5, pp. 1149-1159, May 2006.

- [40] B. Debaillie, et al., "Calibration of Direct-Conversion Transceivers," *IEEE J. Selected Topics in Signal Processing*, Vol. 3, No. 3, pp. 488-498, June 2009.

- [41] P. Rakers, et al., "Multi-mode cellular transceivers for LTE and LTE-Advanced," in *Proc. of IEEE Custom Integrated Circuits Conf.*, pp. 1-8, September, 2014.

- [42] T. Georgantas, et al., "A 13mm<sup>2</sup> 40nm Multiband GSM/EDGE/HSPA+/TDSCDMA/LTE Transceiver," in *IEEE Int. Solid-State Circuits Conf. Dig.*, pp.160-161, 2015.

- [43] V. Petirovic and W. Gosling "Polar-loop transmitter," *IEEE Electronics Letters*, Vol.15, No.10, pp. 286-289, May 1979.

- [44] E. W. McCune Jr. "Multi-mode and Multi-band Polar Transmitter for GSM, NADC, and EDGE," in *IEEE Wireless Comm. & Networking*, pp. 812-815, 2003.

- [45] T. Sowlati, et al., "Quad-Band GSM/GPRS/EDGE Polar Loop Transmitter," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2179-2189, December 2004.

- [46] Y. Akamine, et al., "A Polar Loop Transmitter with Digital Interface including a Loop-Bandwidth Calibration System," in *IEEE Int. Solid-State Circuits Conf. Dig.*, pp.348-349, 2007.

- [47] T. Nakamura, et al., "A Δ∑-Modulator-Less Digitally-Controlled Oscillator using Fractional Capacitors for GSM/EDGE Transmitter," in *2012 Proceedings of the ESSCIRC*. pp. 410-413, Sep. 2012.

- [48] M. Youssef, et al., "A Low-Power GSM/EDGE/WCDMA Polar Transmitter in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 3061-3074, December 2011.

- [49] H. Yang, et al., "A Polar Transmitter Using Interleaving Pulse Modulation for Multimode Handsets," *IEEE Trans. Microwave Theory and Techniques*, vol. 59, no. 8, pp. 2083-2090, August 2011.

- [50] A. Mirzaei, H. Darabi, A. Yazdi, Z. Zhou, E. Chang, and P. Suri, "A 65 nm CMOS Quad-Band SAW-Less Receiver SoC for GSM/GPRS/EDGE," *IEEE J. Solid-State Circuits*, vol. 46, no. 4, pp. 950-964, April 2011.

- [51] O. Olieri, et al., "A multiband multimode transmitter without driver amplifier," in *IEEE Int. Solid-State Circuits Conf. Dig.*, Feb. 2012, pp. 164-165.

第 2 章 周波数シンセサイザの **GSM/ WCDMA/ LTE** フルバンド対応

## 2.1 背景

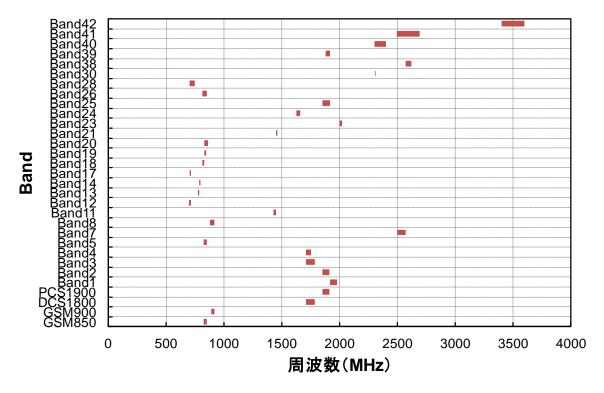

第1章で述べたように、モバイル端末における無線通信のマルチモード、マルチバンド対応が求められている。そのため、局部発振(LO)信号を供給する周波数シンセサイザは、それぞれのモードやバンドに対応した周波数の信号を供給する必要がある。表 2-1 および図2-1、図 2-2 に、移動体通信用の RFIC が対応する必要のあるバンドとその搬送波周波数(図2-1: 送信周波数、図 2-2: 受信周波数)を示した。送信周波数は 699 MHz~3600 MHz、受信周波数は 729 MHz~3600 MHz に渡って各バンドが分布しており、周波数シンセサイザは非常に広い周波数範囲の LO 信号を供給する必要がある。そのためには、源発振信号を供給する電圧制御発振回路(Voltage Controlled Oscillator)は、広い周波数可変範囲で動作する必要がある。

ダイレクト・コンバージョン方式を用いる通常の移動体通信用トランシーバの周波数シンセサイザは、90°位相の異なる2つの信号を生成する必要があるため、周波数シンセサイザを構成する VCO の発振周波数は、搬送波の2倍または4倍に設定される。このような構成を採用することで、VCO プリング(VCO の発振周波数がパワーアンプ出力の周波数に引き込まれてしまう現象)の影響も低減することができる。また、ダイレクト・コンバージョン方式のBB入力および出力のI(In-phase)信号とQ(Quadrature)信号に補正を掛けることによって、90°以外の位相差の信号を用いることができるため、奇数分周回路の適用も原理的には可能である。(奇数分周を用いることによる技術的な課題と解決手段は、3章にて詳説することとし、本章では奇数分周も使用できることを前提に説明する。)

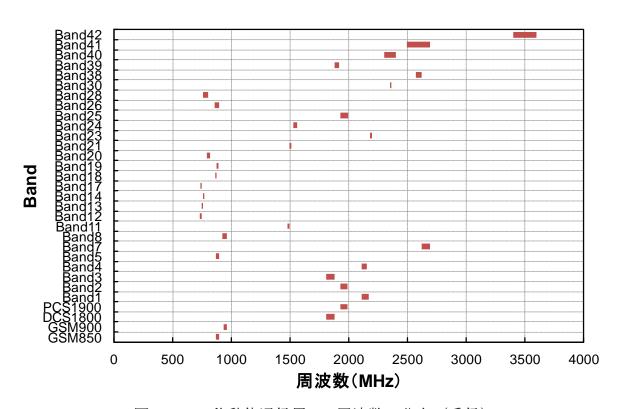

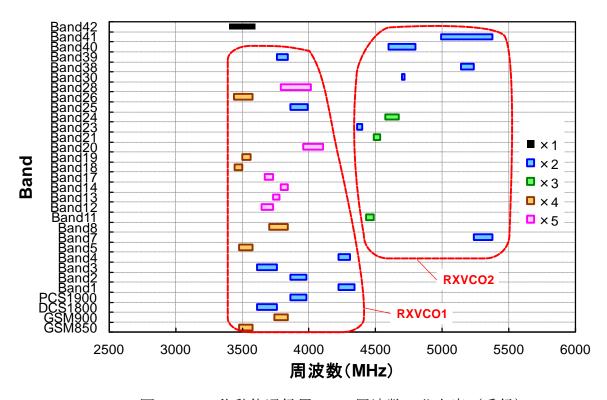

バンドに応じて分周数を変えることで、VCO に必要な周波数可変範囲を縮小することができる。図 2-3 と図 2-4 に、奇数分周を一部に採用した場合に VCO に求められる周波数範囲を示した。送信では 3253 MHz~5380 MHz(周波数可変率(=可変範囲/中心周波数)=49.3%)、受信では 3400 MHz~5380 MHz(周波数可変率=45.1%)の周波数範囲が求められる。このような広い周波数範囲を実現するには、複数の VCO を用いることがまず考えられるが、VCO はプロセス微細化の恩恵を受けにくいインダクタや容量などの受動素子を多用するため、チップ面積が大きくなる問題がある。そのため、できるだけ少ない個数の VCOで上記の周波数範囲をカバーすることが求められる。究極的には送信/受信でそれぞれ一つの VCO で実現することが理想であり、差動制御のバラクタ容量を用いたり[1]、トランスフォーマ結合によるスイッチ制御技術[2-5]を用いたりすることが提案されているが、周波数範囲は広いものの位相雑音が悪いことや VCO 利得が変動することが問題である。

必要な周波数範囲をカバーするために、複数の VCO からなる構成を前提として検討した。 LTE 用バンドで Band 38~Band 42 以外のバンドは、同時に送受信を行う周波数分割複信 (Frequency Division Duplex) 方式であるため、送信/受信で異なる VCO を用いる必要がある。一方 Band 38~Band 42 は送信/受信の周波数が同じ時分割複信 (Time Division Duplex) 方式であるため、VCO は送信/受信で共通化することが可能である。したがって、図 2-3 と図 2-4 に示すように、4 つの VCO (TXVCO1/2, RXVCO1/2) による構成により全てのバンドをカバーすることとした。それぞれの VCO に必要な周波数範囲を表 2-2 に示した。Band 42 に関しては、I/Q 用に位相の異なる LO を供給するには、本来は倍の 7 GHz 以上で発振する VCO を用いる必要がある。したがって、Band 42 が実用化されるまでには、TXVCO1 かRXVCO1 のどちらかを倍の周波数で動作させる必要があるが、本検討では Band 42 を除外して、表 2-2 に示す周波数範囲を目標とし、広い可変範囲が求められる RXVCO1 を実現するための技術を検討した。

表 2-1 移動体通信用バンド

| ·         | 衣.     | <u>2-1</u> 139 | 期 14 地 16 | <u> </u> |        |

|-----------|--------|----------------|-----------|----------|--------|

| 周波数 (MHz) |        |                |           |          |        |

| Band      | 上      | -              | 下         | •        | 国、地域   |

|           | Min.   | Max.           | Min.      | Max.     |        |

| GSM850    | 824    | 849            | 869       | 894      | 北米     |

| GSM900    | 890    | 915            | 935       | 960      | グローバル  |

| DCS1800   | 1710   | 1785           | 1805      | 1880     | グローバル  |

| PCS1900   | 1850   | 1910           | 1930      | 1990     | 北米     |

| Band1     | 1920   | 1980           | 2110      | 2170     | 日、中、欧  |

| Band2     | 1850   | 1910           | 1930      |          | 北米     |

| Band3     | 1710   | 1785           | 1805      | 1880     | グローバル  |

| Band4     | 1710   | 1755           | 2110      | 2155     | 北米     |

| Band5     | 824    | 849            | 869       | 894      | 北米     |

| Band7     | 2500   | 2570           | 2620      | 2690     | 北米、欧、中 |

| Band8     | 880    | 915            | 925       | 960      | 日、欧    |

| Band11    | 1427.9 | 1447.9         | 1475.9    | 1495.9   | 田      |

| Band12    | 699    | 716            | 729       | 746      | 北米     |

| Band13    | 777    | 787            | 746       | 756      | 北米     |

| Band14    | 788    | 798            | 758       | 768      | 北米     |

| Band17    | 704    | 716            | 734       | 746      | 北米     |

| Band18    | 815    | 830            | 860       | 875      | 日      |

| Band19    | 830    | 845            | 875       | 890      | 田      |

| Band20    | 832    | 862            | 791       | 821      | 欧      |

| Band21    | 1447.9 | 1462.9         | 1495.9    | 1510.9   | 田      |

| Band23    | 2000   | 2020           | 2180      | 2200     | 北米     |

| Band24    | 1626.5 | 1660.5         | 1525      | 1559     | 北米     |

| Band25    | 1850   | 1915           | 1930      | 1995     | 北米     |

| Band26    | 814    | 849            | 859       | 894      | 田      |

| Band28    | 703    | 748            | 758       | 803      | 日      |

| Band30    | 2305   | 2315           | 2350      | 2360     | 北米     |

| Band38    | 2570   | 2620           | 2570      | 2620     | 欧、中    |

| Band39    | 1880   | 1920           | 1880      | 1920     | 中      |

| Band40    | 2300   | 2400           | 2300      | 2400     | 中      |

| Band41    | 2496   | 2690           | 2496      | 2690     | 北米、中   |

| Band42    | 3400   | 3600           | 3400      | 3600     | 日      |

図 2-1 移動体通信用 LO 周波数の分布(送信)

図 2-2 移動体通信用 LO 周波数の分布(受信)

図 2-3 移動体通信用 VCO 周波数の分布案(送信)

図 2-4 移動体通信用 VCO 周波数の分布案(受信)

表 2-2 移動体通信用 VCO の周波数範囲

| 古口     | 周波数範囲 (MHz) |      |  |  |

|--------|-------------|------|--|--|

| 項目     | Min.        | Max. |  |  |

| TXVCO1 | 3253        | 4040 |  |  |

| TXVCO2 | 4283.7      | 5140 |  |  |

| RXVC01 | 3400        | 4340 |  |  |

| RXVCO2 | 4360        | 5380 |  |  |

## 2.2 **VCO の**設計

#### 2.2.1 VCO の広帯域化による課題と設計目標

ここでは、VCO の設計目標について説明する。まず発振周波数可変範囲であるが、2.1 節で説明したためここでは割愛する。

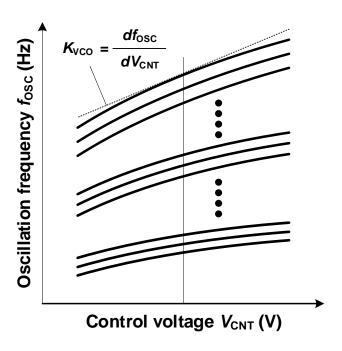

広帯域の VCO を実現するときの背反として、周波数変換利得  $(K_{VCO})$  が変動する問題が ある。周波数シンセサイザを構成する移動体端末用 RFIC の PLL (Phase Locked Loop) では、 3GPPで定められたエミッションマスクを超過しないために、ループ帯域を一定に保つこと が重要である。ループ帯域を一定にすることは、 $K_{VCO}$  とチャージポンプ回路の電流 ( $I_{CP}$ ) の積を一定にすることで実現される[6]ため、 $K_{VCO}$ の変動分を、 $I_{CP}$ を変化させることで補償 できる。しかしながら、移動体通信用の PLL では、位相雑音特性と消費電流の観点から、 許容できる Kvcoの変動分に限界がある。移動体通信用 RFIC の VCO では、広帯域化と低位 相雑音化を両立させるため、図 2-5 に示す特性例の発振周波数調整が行われる[7]。発振周 波数の調整は、2段階で行われる。第1段階は周波数粗調整であり、所望の発振周波数を出 力できる周波数バンドを選択する。第 2 段階は周波数微調整であり、VCO 制御電圧  $V_{tune}$  に より微調整して所望の周波数で固定する。周波数粗調整を行うことで、広帯域化が図られる と共に、 $V_{

m tune}$ 変化量1Vに対する発振周波数の変化量である  $K_{

m VCO}$ を低くできるためLO 信 号の低位相雑音化を図ることができる。LO 信号の位相雑音の要求から、Kvco の上限は 50 MHz/V にする必要があった。一方、 $K_{VCO}$ の下限は、 $I_{CP}$ の電流制限で決定される。 $I_{CP}$ は少 ないほど良く、すなわち 50 MHz/V の  $K_{VCO}$  の時の電流が最適である。 $K_{VCO}$  が変動して低下 してしまうと、Icp はそれに反比例して増大させる必要があるため、余分な電流を流さなけ ればならなくなる。本設計では、 $I_{CP}$ の上限を最適電流の 2 倍とし、25 MHz/V の  $K_{VCO}$ を下 限とした。すなわち、25 MHz/V $\sim$ 50 MHz/V の  $K_{VCO}$ を設計目標とした。

また、移動体端末用 RFIC では消費電流を極力低減することが望まれており、本検討では VCO の目標消費電流を、6 mA 以下とした。また、LO 信号の低位相雑音化のためには、図 2-5 に示した周波数制御を行うことで  $K_{VCO}$  を小さくして周波数制御電圧に含まれる雑音に対す

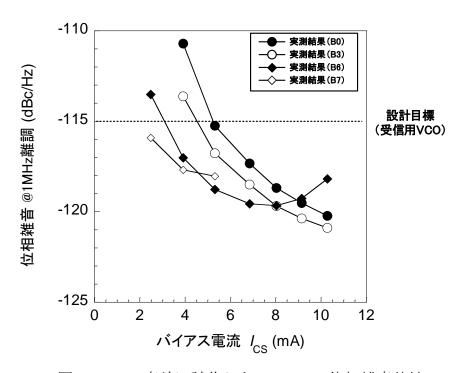

る耐性を高めるだけでなく、VCO 出力自体の位相雑音にも高い性能が求められる。システム設計から導出したVCO出力の位相雑音に対する設計目標は、1~MHz離調時に-115~dBc/Hz以下である。

図 2-5 VCO の周波数制御特性例

図 2-6 VCO の回路構成

## 2.2.2 **VCO** のブロック構成

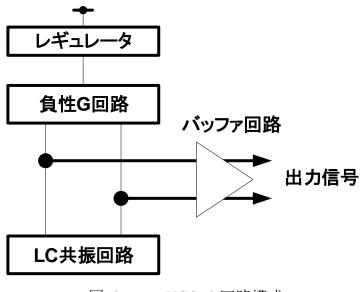

本 VCO の回路構成を図 2-6 に示す。VCO は、VCO コア回路、レギュレータ回路、バイアス回路(図示せず)、バッファ回路から成る。VCO コア回路は、LC 共振回路と負性コンダクタンス生成回路(負性 G 回路)で構成される。レギュレータ回路は、電源電圧変動に対して安定した電圧を供給する回路であり、VCO に要求される低い周波数変動(2.5 V~3.0 V の電源電圧変動に対して 0.5 MHz 以下)を実現するために用いている。本設計で用いたレギュレータ回路は、2.5 V~3.0 V の電源電圧変動範囲に対して、2.45 V の電圧を変動範囲 10 mV 以下で VCO コア回路へ供給することができる。バイアス回路は、電源電圧、温度の変動に対して安定なバイアス電圧を VCO コア回路へ供給する回路である。

#### 2.2.3 共振回路の設計

本 VCO における共振回路には、Si 基板上への集積化が可能なことから、インダクタ(インダクタンス L)と容量(容量値 C)からなる LC 共振回路を用いた。このとき発振周波数は以下の式(2-1)で表される。

$$f_{OSC} = \frac{1}{2\pi\sqrt{LC}} \tag{2-1}$$

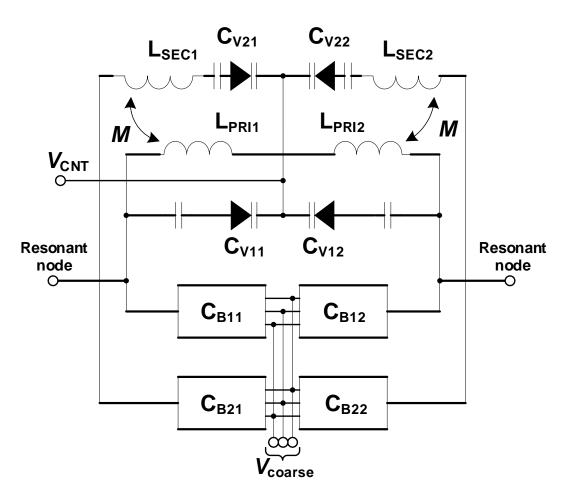

共振回路の構成は、周波数変換利得( $K_{VCO}$ )の設計目標を達成するため、可変インダクタ構成を用いた周波数変換利得変動の抑制技術[3]を適用した構成(図 2-7)を採用した。共振回路は、相互インダクタンス M を介して結合した主インダクタ( $L_{PRI}$ )、副インダクタ( $L_{SEC}$ )と、それぞれのインダクタに接続された容量バンク  $C_{B1}$ 、 $C_{B2}$  および pn 接合バラクタ容量  $C_{V1}$ 、 $C_{V2}$  で構成される。 $C_{B1}$ 、 $C_{B2}$  は、ともに 3 ビットの MOS バラクタ容量で構成され、それぞれのビットの MOS バラクタ容量の容量値を周波数粗調整制御電圧により 2 段階に制御することで、8 (= $2^3$ ) バンドの周波数バンドを設定できる。MOS バラクタには、ゲートサイズがゲート長  $1.1~\mu m$ 、ゲート幅  $5.4~\mu m$  であり、4~GHz での Q 値が 15~Oものを用いた。周波数微調整は、pn 接合バラクタ容量  $C_{V1}$ 、 $C_{V2}$  の容量値を制御電圧  $V_{tune}$  により連続的に制御することで行われる。このとき  $K_{VCO}$  は以下の式(2)で表される。

$$K_{VCO} = \frac{1}{4\pi} \cdot \frac{\left(L_{eff} - L_{p}\right)^{2}}{\sqrt{L_{eff}} M^{2}} \cdot \frac{\sqrt{C_{V1} + C_{B1}}}{{C_{V2}}^{2}} \cdot \frac{dC_{V2}}{dV_{tune}}$$

(2-2)

ここで $L_{\rm eff}$ 、 $L_{\rm P}$ 、M、 $C_{\rm V1}$ 、 $C_{\rm V2}$ 、 $C_{\rm B1}$  は、それぞれ実効的なインダクタンス、主インダクタの自己インダクタンス、主インダクタと副インダクタ間の相互インダクタンス、主インダクタ側の pn 接合バラクタ容量の容量値、副インダクタ側の pn 接合バラクタ容量の容量値、主インダクタ側の容量バンクの容量値である。 $L_{\rm eff}$  と  $C_{\rm M1}$  を調整することで、 $K_{\rm VCO}$  を周波数バンドに依らずほぼ一定にすることができる。

図 2-7 VCO の共振回路の構成

## 2.2.4 VCO の回路形式の検討

本設計は  $0.4~\mu m$  Si BiCMOS プロセスでの試作を前提としており、4~GHz 帯での発振回路としては MOS トランジスタのゲート長が長い。そのため MOS トランジスタのみで構成した VCO は、MOS トランジスタの電流利得が BJT に比べて低く、特に高温( $85^{\circ}$ C)時において発振停止が問題であった。発振停止を避けるためにはバイアス電流を増加させる必要があり低消費電力化に適さないため、MOS トランジスタのみを用いた構成は今回の検討からは外した。

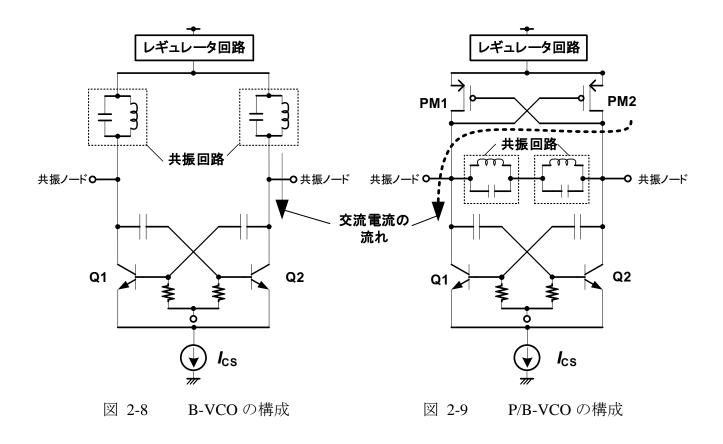

図 2-8 は負性コンダクタンス生成回路に BJT のみを用いた VCO (B-VCO)、図 2-9 は PMOS トランジスタ (PMOS) と BJT を用いた VCO (P/B-VCO) の回路構成[8]である。 PMOS を用いると、交流電流は図 2-9 の矢印に沿って流れるため、共振回路のインピーダンスを擬似的に 2 倍にできる。そのため振幅を BJT-VCO の振幅の約 2 倍にでき、同等の振幅を得るための電流を半分にできるため低消費電力化が期待できる。

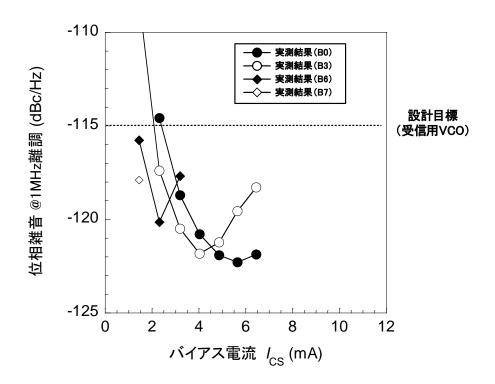

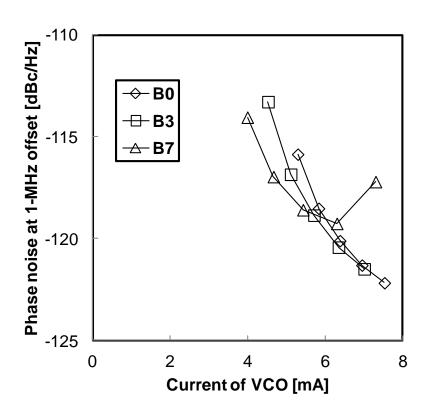

回路構成検討のために事前に試作した VCO の 1 MHz 離調時の位相雑音特性のバイアス電流依存性を図 2-10 と図 2-11 に示す。特性線が 4 本あるが、それぞれ周波数バンドが異なる。これらの VCO では 8 つの周波数バンドを設定できるように設計してあり、周波数の低い周波数バンドから順に B0、B1、・・B7 と称する。図には、B0、B3、B6、B7 の位相雑音特性を示した。位相雑音のバイアス電流特性は以下のように説明できる。まず、バイアス電流の増大とともに振幅が大きくなり位相雑音特性が向上する。一方で振幅が過大となると発振波形が歪み、BJT の共通エミッタでの発振周波数の 2 倍高調波成分が大きくなる。電流源の低周波雑音はこの 2 倍高調波近辺にアップコンバートされ、さらに共振回路で発振周波数と混合されて発振周波数近傍に位相雑音として重畳する。その結果、バイアス電流を増大させると位相雑音が悪化する。すなわち、位相雑音の観点で最適な電圧振幅が存在し、実測結果とシミュレーション結果から解析すると 900 mVpp 程度が最適振幅であることがわかった。

B-VCO と P/B-VCO の位相雑音特性を比較すると、B-VCO の位相雑音(図 2-10)は良好であるが、低周波バンドで所望の位相雑音特性を得るには大きなバイアス電流(>5.5 mA)が必要になる問題がある。一方 P/B-VCO の位相雑音(図 2-11)は、B-VCO よりも振幅を大きくできるため、低周波バンドでも小さいバイアス電流(<2.5 mA)で所望の特性を得られる。しかし、高周波で位相雑音が悪化するだけでなく位相雑音のバイアス電流依存性が急峻となる問題がある。バイアス電流は抵抗やトランジスタのプロセスばらつきで変動してしまうため、ロバスト性を考慮すると位相雑音のバイアス電流依存性は緩やかであることが望まれる。プロセスばらつきによるバイアス電流の変動を回路シミュレーションにより求めると±15%であると想定できるので、その範囲内で目標の位相雑音特性を達成する必要がある。このように、従来の回路構成を用いると、低周波バンドにおいて消費電流が増大するか、

高周波バンドにおいて位相雑音が増大し、かつバイアス電流に対する位相雑音特性の安定度

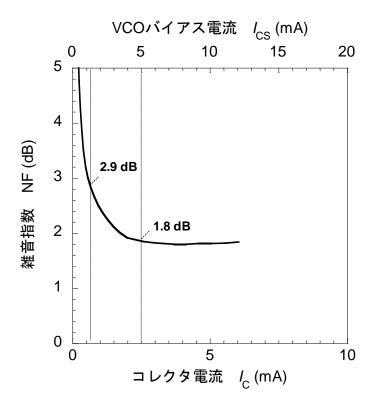

が低下する問題があった。その原因について、BJT の雑音指数(NF)と帯域内における共振回路のインピーダンス変動の観点から解析した。本設計の VCO では、インダクタンス Lが 380 pH のインダクタを用いている。共振回路の Q 値( $Q_{RES}$ )は、MOS バラクタの Q 値を考慮すると、3.3 GHz で 10、4.4 GHz で 16 となる。さらに、共振回路のインピーダンス  $Z_{RES}$  ( $=\omega LQ_{RES}$ ) は周波数に比例するため、広帯域の周波数可変範囲を必要とする本報告の VCOでは帯域内で大きく変動し、3.3 GHz では  $90\Omega$  であるのに対し、4.4 GHz で 160  $\Omega$  と 1.8 倍まで増大する。

以上のインピーダンスの変動を踏まえて、それぞれの VCO で最適振幅となるバイアス電流について考察する。 $3.3~{\rm GHz}$  時でバイアス電流を $5~{\rm mA}$  に設定した場合、 ${\rm B-VCO}$  では $450~{\rm mVpp}$  の振幅しか得られないが、 ${\rm P/B-VCO}$  では、 ${\rm B-VCO}$  の約 $2~{\rm fe}$  の振幅となるため 900 mVpp となり、最適な振幅となる。 ${\rm B-VCO}$  で振幅を最適化するには、バイアス電流を $10~{\rm mA}$  まで増大させる必要がある。-方  $4.4~{\rm GHz}$  時でバイアス電流を $5~{\rm mA}$  に設定した場合、 ${\rm B-VCO}$  では振幅は $800~{\rm mVpp}$  となり位相雑音が最小になる最適振幅( $=900~{\rm mVpp}$ )程度であるが、 ${\rm P/B-VCO}$  では $1600~{\rm mVpp}$  と過大である。 ${\rm P/B-VCO}$  で振幅を最適化する( $900~{\rm mVpp}$  程度にする)にはバイアス電流を $2.5~{\rm mA}$  まで低減させる必要がある。しかしながら、バイアス電流を低減しすぎると、 ${\rm BJT}$  の  ${\rm NF}$  が悪化することにより位相雑音が悪化する。

図 2-12 は、シミュレーションにより求めたエミッタ接地 BJT (エミッタサイズ  $0.2 \times 2.8 \, \mu m$  の BJT を  $16 \, \dot{u}$  列)の  $4.4 \, GHz$  における NF のコレクタ電流依存性である。BJT の並列数は VCO を構成する差動対の片方の並列数であるため、VCO のバイアス電流に換算するには横軸のコレクタ電流を倍にして考えれば良い。図 2-12 で上の横軸に VCO のバイアス電流に相当する電流を示した。ポートのインピーダンスは共振回路のインピーダンスに等しい  $160 \, \Omega$  の純抵抗とした。NF は VCO バイアス電流  $5 \, mA$  で  $1.8 \, dB$  とほぼ最小値を示すが、 $2.5 \, mA$  では  $0.5 \, dB$  悪化して  $2.3 \, dB$  となってしまう。図 2-11 に示した位相雑音特性では、P/B-VCO において最高周波バンドで位相雑音が最小になるのはバイアス電流が  $1.3 \, mA$  のときであり、この場合 NF は  $2.9 \, dB$  になり  $5 \, mA$  での NF に比べて  $1.1 \, dB$  悪化する。高周波バンドでは振幅を最適化しても NF が悪化するため、位相雑音が悪化してしまう。以上より、VCO 帯域内でのインピーダンス変動が原因で、全帯域で振幅と BJT の NF を最適化することが困難となり、位相雑音の悪化、または消費電流の増大を招くことが明らかとなった。次節にて、全帯域で低位相雑音と低消費電流を両立するために考案した新規の実効インピーダンス制御技術を用いた負性コンダクタンス生成回路について述べる。

図 2-10 事前に試作した B-VCO の位相雑音特性

図 2-11 P/B-VCO の位相雑音特性

図 2-12 バイポーラ・トランジスタ(エミッタ面積= $0.2 \times 2.8 \mu m$ )の雑音指数の シミュレーション結果

#### 2.2.5 負性コンダクタンス生成回路の設計

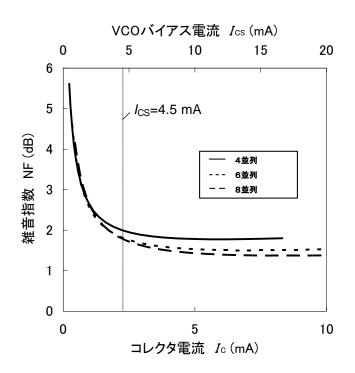

低周波バンドでの低電流化と、高周波バンドでの低位相雑音化を同時に実現するため、振幅と NF を同時に最適化する方法について検討した。受信用 VCO に許容される消費電流は 6 mA であり、レギュレータ回路とバイアス回路で 1.5 mA 消費されるため、VCO のバイアス電流は 4.5 mA 以下で設計されなければならない。図 2-13 は、エミッタサイズが  $0.2 \times 6$   $\mu$ m × 2 で並列数が 4、6、8 の BJT における NF のコレクタ電流依存性シミュレーション結果である。ポートのインピーダンスは共振回路のインピーダンスに等しい 160  $\Omega$  の純抵抗とした。図 2-12 と同様に、VCO のバイアス電流に相当する電流を上の横軸に示した。NF が最小になるのは、並列数 4、6、8 の場合でそれぞれ 12、14、17 mA の時であり、4.5 mA で最小にはならないが、4.5 mA 近傍では、並列数を増大するに従い NF が小さくなる。しかしながら並列数 6 と 8 の場合の 4.5 mA での NF の差はわずか 0.03 dB である。BJT の並列数を増大すると寄生容量が増大して周波数可変範囲が縮小するため、BJT の並列数は 6 とした。

図 2-13 バイポーラ・トランジスタの雑音指数のシミュレーション結果 (並列数依存性)

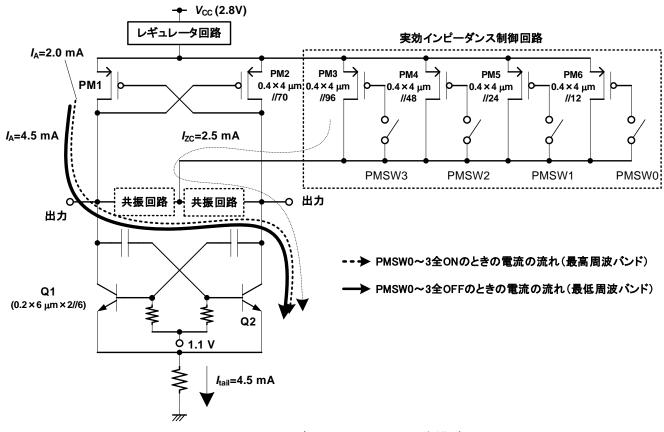

次に、 $4.5 \, \text{mA}$  のバイアス電流で振幅を  $900 \, \text{mVpp}$  程度に最適化する方法を述べる。上述したように、高周波では振幅が大きくなり過ぎ、低周波では振幅が小さくなり過ぎる問題がある。これを解決するため、高周波バンドでは共振回路のインピーダンスを小さく、低周波バンドでは共振回路のインピーダンスを小さく、低周波バンドでは共振回路のインピーダンス制御技術を提案した。図 2-14 に提案した実効インピーダンス制御技術を用いた VCO の回路構成を示す。提案回路は、低電流動作が可能な従来の P/B-VCO の回路構成に、PMOS を用いた実効インピーダンス制御回路を追加している。実効インピーダンス制御回路の PMOS スイッチ (PMSW0~PMSW3) を切り替えることで、増幅部の PMOS (PM1、PM2) に流れる電流を調整し、実効的な共振回路のインピーダンスを制御することができる。図 2-14 の回路の動作を説明する。増幅部 PMOS (PM1、PM2) のゲート幅の総和を  $W_A$  ( $\mu$ m) とし、実効インピーダンス制御回路中でオンしている PMOS のゲート幅の総和を  $W_{ZC}$  ( $\mu$ m) とすると、PM1 (または PM2) を流れる電流  $I_{A}$  と実効インピーダンス制御回路を流れる電流  $I_{CC}$  は、VCO のバイアス電流  $I_{Iail}$  を用いて以下の式で表される。

$$I_A = \frac{W_A}{W_A + W_{ZC}} \cdot I_{tail} \tag{2-3}$$

$$I_{ZC} = \frac{W_{ZC}}{W_A + W_{ZC}} \cdot I_{tail} \tag{2-4}$$

このとき VCO の発振電圧振幅は、共振回路のインピーダンスを  $Z_{RES}(\omega)$ とすると、

$$A_{VCO} = 2Z_{RES}(\omega) \cdot \frac{W_A}{W_A + W_{ZC}} \cdot I_{tail} + Z_{RES}(\omega) \cdot \frac{W_{ZC}}{W_A + W_{ZC}} \cdot I_{tail}$$

$$= \left(1 + \frac{1}{1 + W_{ZC}/W_A}\right) \cdot Z_{RES}(\omega) I_{tail} = Z_{RES}(\omega)' I_{tail}$$

(2-5)

となる。式(2-5)より、 $W_{ZC}$ を切り替えることで、実効的な共振回路のインピーダンス( $Z_{RES}(\omega)$ )を切り替えることができ、その結果振幅を制御することができることがわかる。すなわち、周波数が高くなるにしたがって実効インピーダンス制御回路の PMOS スイッチ(PMSW0~PMSW3)を短絡して  $W_{ZC}$ を大きくすれば、周波数の上昇にともない  $Z_{RES}(\omega)$ 'を小さくすることができる。また中間の周波数バンドでは、周波数バンドの切り替えに連動して PMSW0から PMSW3 の複数のスイッチの導通状態を細かく制御することで、最高周波バンドと最低周波バンドの中間特性を示すように設定した。図 2-14 の回路構成を用いることで、広帯域の可変範囲が必要な VCO でも全ての周波数で低位相雑音を実現することが可能となった。

図 2-14 提案した VCO の回路構成

### 2.2.6 レイアウト設計

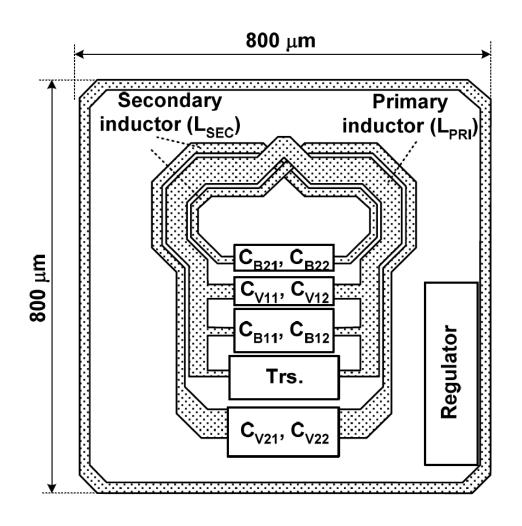

上述した  $K_{VCO}$ 変動補償機能および温度補償機能を備えた共振回路と、負性コンダクタンス生成回路を、配線による損失と占有面積をできるだけ小さくできるように配置を検討した。図 2-15 にレイアウト構成を示す。占有面積は、 $800\times800~\mu m$  である。

図 2-15 提案した VCO のレイアウト構成

# 2.3 **VCO の評価**

試作した受信用 VCO の特性は、RFIC をパッケージングした後、VCO 用電源電圧端子に漏洩する信号をオンボードで測定して取得した。発振周波数制御特性、位相雑音特性共に、 $10\,\mathrm{MHz}\sim7\,\mathrm{GHz}$  の周波数範囲を持つ Keysight Technologies 社製シグナル・ソース・アナライ

ザ E5052A を用いて測定した。また、提案した周波数変換利得変動抑制技術を適用していない VCO も、比較のために試作した。具体的には、図 2-7 において  $L_{SEC}$ 、 $C_{V2}$ 、 $C_{B2}$ を用いない VCO を従来 VCO として試作した。

# 2.3.1 周波数可変範囲と周波数変換利得

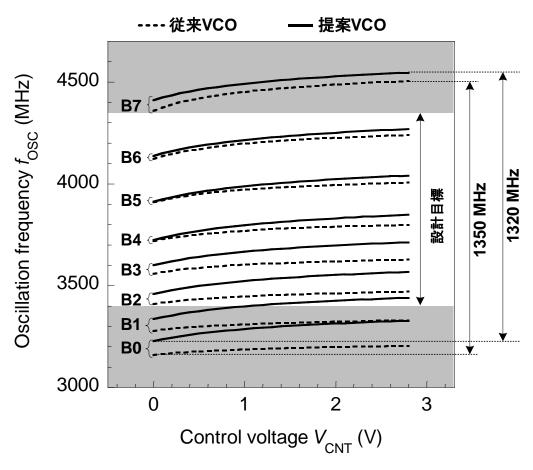

図 2-16 は VCO の周波数制御特性である。図 2-16 には 8 本の周波数バンドのみ示してあり、説明のため周波数の低い周波数バンドから順に、B0、B1、・・B7 と称する。 $V_{tune}=0$  V  $\sim$ 2.8 V において得られる周波数可変範囲は、 $3220\sim$ 4540 MHz( $\triangle f=1320$  MHz、設計目標 >940 MHz)であり、搬送波供給に必要な周波数範囲をカバーでき、かつ設計目標以上の周波数可変範囲を達成した。

図 2-16 提案した VCO の周波数制御特性

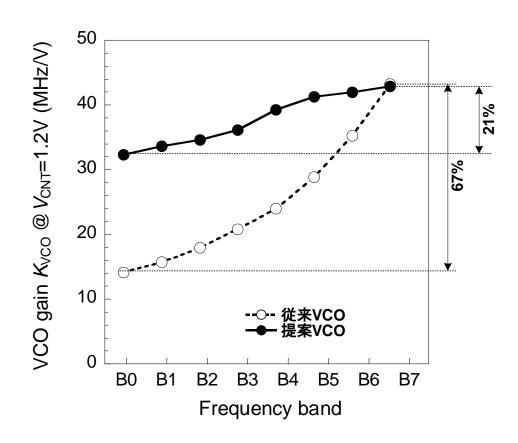

図 2-17 は、 $V_{\text{tune}}$ = 1.2 V における周波数変換利得の周波数バンド依存性である。従来 VCOでは最大周波数バンド (B7) で 43 MHz/V であるが、最小周波数バンド (B0) では 14 MHz/V まで 67%も低下し、設計目標の 25 MHz/V を下回ってしまう。一方提案 VCO では、最小周波数バンドでも 32 MHz/V と最大値から 21%の低下に抑えられ、全周波数バンドにおいて設計目標の 25~50 MHz/V の変動範囲内に収まっており、 $K_{\text{VCO}}$ 変動抑制技術の有効性を確認した。以上より、周波数制御特性、 $K_{\text{VCO}}$ 共に設計目標を達成した。

図 2-17 提案した VCO の周波数変換利得( $V_{\text{tune}} = 1.2 \text{ V}$ )

#### 2.3.2 位相雑音特性

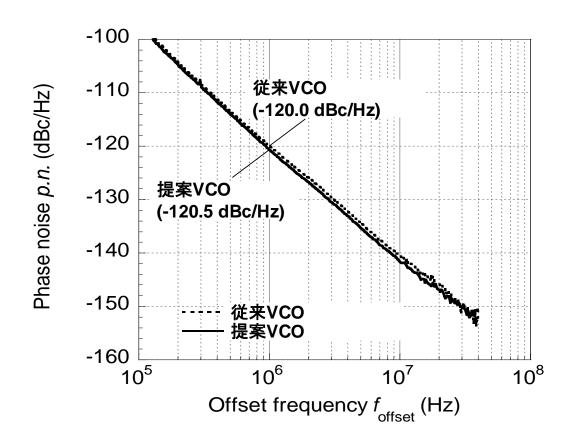

図 2-18 に、VCO の位相雑音特性を示す。1 MHz 離調時には、-120.5 dBc/Hz であり、設計目標(<-115 dBc/Hz)を達成した。図 2-19 に VCO の 1 MHz 離調時の位相雑音の消費電流依存性を示す。図 2-19 には、最低周波バンド B0、中心バンド B3、最高周波バンド B7における位相雑音を示した。全ての周波数バンドにおいて設計目標の位相雑音特性(<-115 dBc/Hz @1 MHz 離調、<6 mA)を達成できた。さらに、課題であった高周波バンドにおける位相雑音のバイアス電流依存性も、±1 mA のバイアス電流変動に対して位相雑音変動が1.2 dB であり、バイアス電流に対する安定性も向上させることができた。以上の評価結果より、新規の実効インピーダンス制御技術を導入した提案回路は、課題であった低周波バンドでの低電流化と、高周波バンドでの位相雑音低減と消費電流に対する安定化を実現し、消費電流と位相雑音特性に対する設計目標を達成できた。

図 2-18 VCO の位相雑音特性の測定結果

図 2-19 提案した VCO の位相雑音の消費電流依存性

### 2.3.3 性能比較

本論文で述べた VCO の実測性能を、他の広帯域 VCO の報告例と比較した(表 2-3)。表 2-3 中の周波数可変率は、制御電圧範囲全体を使用した周波数可変量の中心周波数に対する比率である。ここで便宜上、式(2-6)に示す評価指数(Figure of Merit: FOM)を用いて水準比較を行う。

$$FOM = pn + 10\log\left\{ \left( \frac{f_{offset}}{\Delta f} \right)^{2} P_{DC} / 100 \right\}$$

(2-6)

ここで pn、 $f_{offset}$ 、 $P_{DC}$ 、 $\Delta f$  は、それぞれ 1 MHz 離調における位相雑音、離調周波数[Hz]、 VCO コア回路の消費電力[mW]、周波数可変範囲[Hz]である。FOM は、1MHz 離調の位相雑音に加えて、VCO コア回路で消費される電力と周波数可変範囲を含めて評価できる指標であり、値が低いほど良好な性能であることを意味する。

本研究の VCO は、トップレベルの FOM を達成しているだけでなく、周波数変換利得の変動を抑圧することもできており、より実用的な VCO であると言える。

発振 周波数 位相雑音 プロセス Ref. 消費電力 **FOM** 周波数 可変率 (1MHz 離調) 単位 **GHz** dBc/Hz mWdBc/Hz % 130nm 59 4.85 -1093.0 -193[1] **CMOS** [9] 4.85 22 -12230.0 -188Si BJT  $0.25 \mu m$ [10] 3.70 23 -1177.5 -187**CMOS** -19965 nm 77 -121(周波数ギャ 4.05 14.2 [11] **CMOS** ップあり) 65 nm 8.4 3.48 16 -122-188[12] **CMOS**  $0.4 \mu m$ 本研究 3.9 -12034 11.2 -192**BiCMOS**

表 2-3 開発した VCO の性能比較

## 2.4 まとめ

移動体通信用 RFIC で用いる受信用 VCO を開発した。開発した VCO は、必要な広帯域特性を実現しただけでなく、広帯域化を行った際に問題となる周波数変換利得  $K_{VCO}$  の変動を 21%まで低減することができた。また、位相雑音も十分に抑圧することができており、マルチバンド、マルチモード対応 RFIC に適した VCO を開発することができた。

また、本章で述べた VCO は BiCMOS プロセスにて試作したが、提案した技術は配線を用いたトランスフォーマやバラクタ容量などの受動素子を用いた共振回路の構成である。したがって、移動体通信用 RFIC で用いられる CMOS プロセスにおいても適用することが可能であり、以降で述べる第 3 章、第 4 章で述べた技術とともに同じ RFIC へ適用することができる。

## 参考文献

- [1] N. H.W. Fong, et. al., "A 1-V 3.8-5.7 GHz Wideband VCO with Differentially-Tuned Accumulation MOS Varactors for Common-Mode Noise Rejection in CMOS SOI Technology," *IEEE Trans. On Microwave Theory and Techniques*, Vol. 51, No. 8, Aug. 2003.

- [2] L. K. Leung, W. C. Chui, and H. C. Luong, "A 1V Dual-Band VCO Using an Integrated Variable Inductor," in *Asian Solid-State Circuits Conference*, pp. 273-276, November 2005.

- [3] T. Nakamura, T. Masuda, A. Kodama and K. Washio "A variable inductor using mutual-current control and application to a SiGe 4.5-GHz VCO for wide tuning range", in *Proc. Asia Pacific Microw. Conf.*, 2005.

- [4] U. Decanis, et al. "A low-noise quadrature VCO based on magnetically coupled resonators and a wideband frequency divider at millimeter waves", *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp.2943 -2955 2011.

- [5] X. Geng and F. F. Dai "An X-Band Transformer-Coupled Varactor-Less Quadrature Current-Controlled Oscillator in 0.18 um SiGe BiCMOS Technology", *IEEE J. Solid-State Circuits*, vol. 45, pp.1669 -1677 2010.

- [6] C. Lam and B. Razavi "A 2.6-GHz/5.2-GHz Frequency Synthesizer in 0.4-μm CMOS Technology", *IEEE J. Solid-State Circuits*, vol. 35, no. 5, pp.788 -794 2000.

- [7] A. Kral, F. Behbahani, and A. A. Abidi, "RF-CMOS Oscillators with Switched Tuning," in *Proc. of IEEE Custom Integrated Circuits Conf.*, September, 1998, pp. 555-558.

- [8] N. Itoh, et. al., "Integrated LC-tuned VCO in BiCMOS process," in *Proc. of the 27th 2001 European Solid-State Circuits Conference*, pp. 344-347, September, 2001.

- [9] T. Copani, S. A. Smerzi, G. Girlando and G. Palmisano "A 12-GHz Silicon Bipolar Dual-Conversion Receiver for Digital Satellite Applications", *IEEE J. Solid-State Circuits*, vol. 40, no. 6, pp.1278 -1287 2005.

- [10] J. Maget, M. Tiebout, and R. Kraus, "Influence of Novel MOS Varactors on the Performance of a Fully Integrated UMTS VCO in Standard 0.25-μm CMOS Technology", *IEEE J. Solid-State Circuits*, vol. 37, pp.953 -958 2002.

- [11] G. Li, L. Liu, Y. Tang and E. Afshari "A Low-Phase-Noise Wide-Tuning-Range Oscillator Based on Resonant Mode Switching", *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp.1295-1308 2012.

- [12] S. Dal Toso, A. Bevilacqua, M. Tiebout, N. Da Dalt, A. Gerosa and A. Neviani "A 0.06 mm<sup>2</sup> 11 mW Local Oscillator for the GSM Standard in 65 nm CMOS", *IEEE J. Solid-State Circuits*, vol. 45, no. 7, pp.1295 -1304 2010.

第3章 送信回路

## 3.1 背景

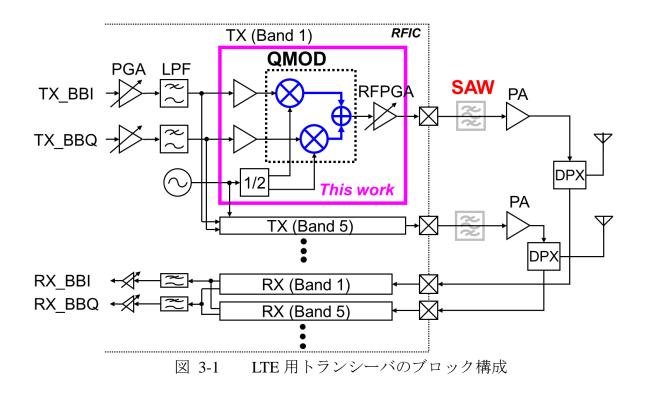

第1章で述べたように、マルチモード・マルチバンド対応の通信モジュールの小型化には、部品点数の削減が必要であり、特に SAW フィルタとバラン(Balance to Unbalance)の削減が求められている。送信用 SAW フィルタは、送信信号に重畳した雑音が送信帯域外、特に受信帯域に漏洩することを防止するために用いられている。したがって SAW フィルタを削減するには、送信出力の受信帯域における雑音の低減が不可欠となる。図 3-1 に LTE 用トランシーバのブロック構成を示す。送信回路の中で最も考慮すべき雑音源は、PLL と直交変調器(Quadrature MODulator)である。PLL については、第2章で述べた広帯域化技術や、ADPLL(All Digital PLL)技術[1]に取り組むことによって、許容される消費電流で低雑音の広帯域 PLL が実現される。QMOD に関しては、低雑音であるとともに、高い線形性と低い消費電力が求められる。Farazian 等[2]は、スイッチ・トランスコンダクタンス・ミキサを用いた送信回路によって低雑音を実現しているが、消費電力が大きい問題がある。その他には、2 倍周波数の LO を用いてエッジをマスクする技術[3]や、25%デューティの LO を用いる技術[4-9]が用いられており、SAW フィルタレス送信機に適用可能な性能を示している。しかしながら、これらの技術では LO タイミングやデューティサイクルの調整のために回路を追加する必要があるため、消費電力が増大する問題がある。

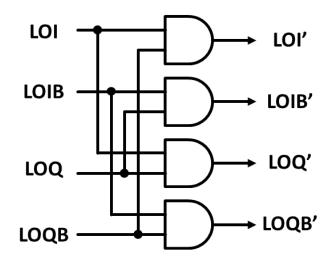

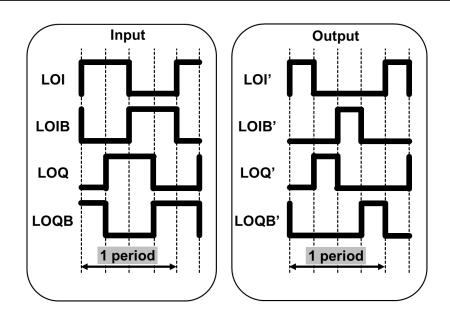

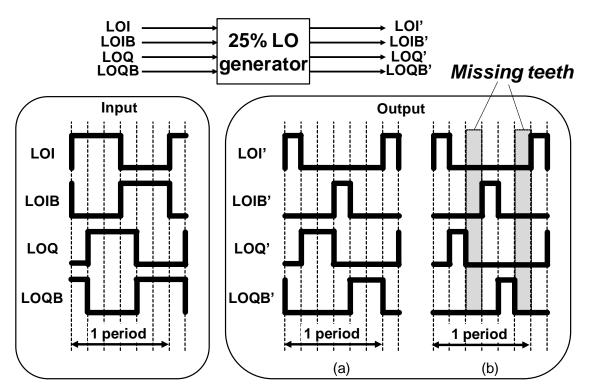

さらに、2.1 節で述べた奇数分周を用いた周波数シンセサイザを用いる場合には、25%デューティのLO技術には新たな問題が発生する。第2章で述べたように、奇数分周の適用[10]は、周波数シンセサイザを構成する VCO の周波数可変範囲の仕様を緩和し、VCO の個数を削減してチップサイズを低減するために不可欠である。しかしながら、奇数分周の出力を用いた場合には、最適な 25%デューティのLO信号を作成することは困難であることが以下に述べる検討により明らかとなった。図 3-2 は、一般的な 25%デューティ LO を作成する回路(25%LO 生成器)の構成である。2 分周や 4 分周などの偶数分周で作成された信号を入力した場合の出力は図 3-3 のようになり、25%のデューティサイクルが実現される。一方、例えば 3 分周器で作成された信号を 25%LO 生成器に入力した場合には、図 3-4(a)または(b)に示すような出力が得られてしまう。(a)では、I (In-phase)信号用 LO (LOI、LOIB)と Q (Quadrature)信号用 LO (LOQ、LOQB)のデューティが異なっており、(b)では、4 相の全ての LO がローとなる期間が発生する。このような LO 信号を用いると、I 信号と Q 信号の利得が異なるため、イメージ信号抑圧比(Image Rejection Ratio)が低下したり、IRR を補正するために線形性が低下したりする問題が発生してしまう。以上のような経緯から、奇数分周回路を用いた場合にも低雑音かつ低消費電力である QMOD を開発する必要があった。

バランは差動信号をシングルエンド信号に変換する受動素子であるが、通信モジュール基板からのバラン素子の削減には、バランを RFIC に内蔵することが必要である。バランを RFIC に内蔵することで、バラン素子を削減できるだけでなく、RFIC のピン数も削減できる利点もあるが、RFIC の面積は増大してしまう。オンチップ・バランの報告例[1-9]は多数あるが、占有面積が大きい問題がある。占有面積削減のため、スパイラル型バラン[3-9, 11]やスローウェーブ・マイクロストリップラインを用いたマーチャンド・バラン[12]などが開発されており占有面積が削減されているものの、さらなる面積の低減が必要である。

図 3-2 25%デューティ LO 生成回路の構成例

図 3-3 偶数分周出力を用いた場合の 25% LO 信号の波形

図 3-4 奇数分周出力を用いた場合の 25% LO 技術の問題点

## 3.2 LTE 用送信機の設計

### 3.2.1 **LTE** 用送信機プロトタイプ

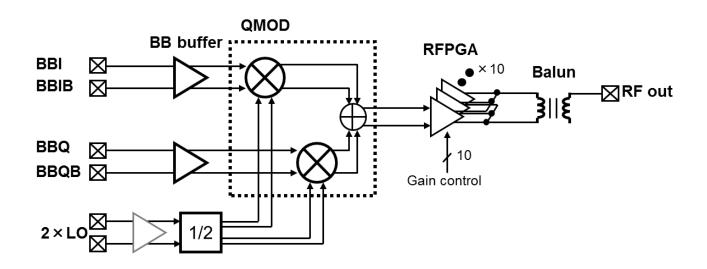

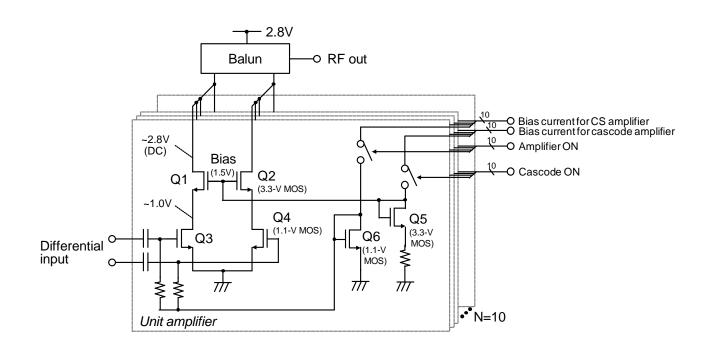

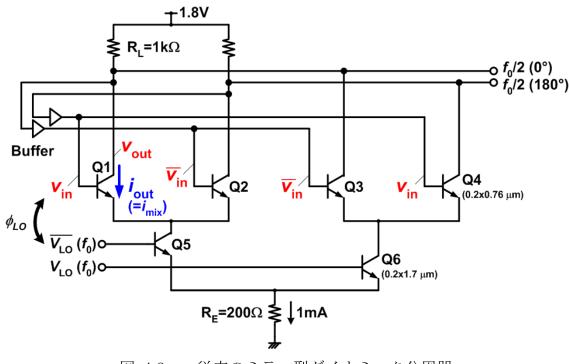

図 3-1 は、想定している LTE フルバンド対応の SAW レス・トランシーバのブロック構成である。RFIC の TX 出力ポートと PA の間にある SAW フィルタを削除するためには、送信出力の受信帯域における雑音を-158 dBc/Hz 以下(この値はデュプレクサのアイソレーションに依存するが、ここでは 45 dB として換算)に抑圧しなければならない。本設計では、プロトタイプの送信機として、図 3-5 に示すバンド 1 対応の送信機を開発した。開発した送信機は、1/2 周波数分周器、ベースバンド用バッファ回路(BB バッファ回路)、QMOD コア回路、RF-PGA(Programmable Gain Amplifier)、バランで構成される。BB バッファ回路はソースフォロワ回路で構成され、周波数分周器は低雑音のロジックタイプ分周器を用いた。RF-PGA は 10 並列のユニット増幅器で構成され、アクティブなユニット増幅器の個数を制御することで利得を調整することができる。

図 3-5 開発した LTE バンド 1 用送信回路

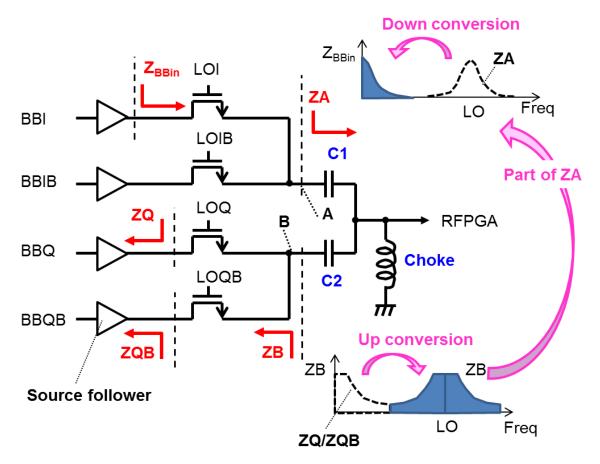

#### 3.2.2 **QMOD** コア回路

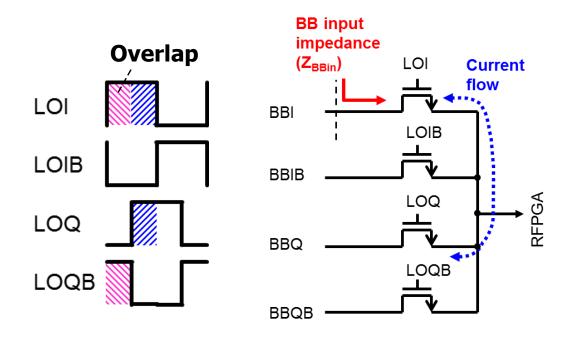

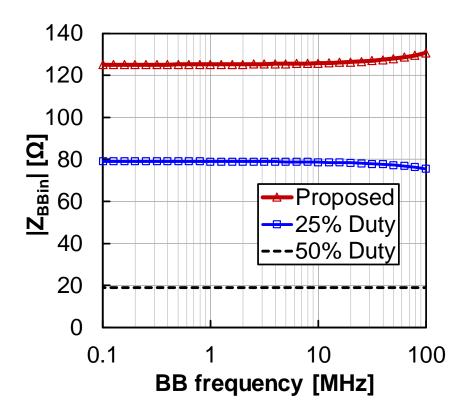

低雑音の QMOD を実現するには、受動型の QMOD が適している。図 3-6 に、従来の受動型 QMOD の回路構成を示す。従来の受動型 QMOD は低雑音特性を示すものの、線形性が低い問題がある。線形性が低い主な原因は、図 3-6 に点線で示したような貫通電流が存在するためである。従来の QMOD では、LOI と LOQ が同時にハイになる期間があり、この期間中は LOI と LOQ が駆動する NMOS が同時にオンになる。そのため、BBI と BBQ 間のインピーダンスが低下する。この同時オンによって、BB バッファから見た QMOD の入力インピーダンスが低下するため、線形性を保つためには BB バッファの消費電力を増大して駆動力を向上させる必要がある。図 3-7 は、回路シミュレーションにより求めた BBI から見た入力インピーダンス( $Z_{BBin}$ )の周波数依存性である。LO 信号の周波数はバンド 1 の 1950 MHz に設定した。 $Z_{BBin}$  は、わずか 19 Q である。 $Z_{BBin}$  を増大させるには、25% デューティ LO 技術は非常に有効である。図 3-7 には、25% LO を用いた時の  $Z_{BBin}$  も示している。 $Z_{BBin}$  は 79 Q であり、約 4 倍に増大させることができる見通しである。しかしながら、25% LO 技術は、25% LO 生成器が必要になることから消費電力が増加するだけでなく、奇数分周を用いて生成された LO 信号を用いた時に IRR や線形性に問題が発生してしまう。

図 3-6 従来の受動ミキサの回路構成と問題点

図 3-7 受動ミキサをベースバンド・バッファから見たときの入力インピーダンス

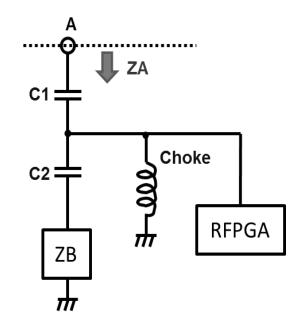

そこで、図 3-8 に示すような、容量を用いて I 信号と Q 信号を合成する回路構成を提案した。I 信号と Q 信号の間に容量(C1 と C2)を挿入することによって、低周波の信号は I/Q 間でアイソレートされると考えられる。その結果、 $Z_{BBin}$  は増大することが期待される。単純な直列回路と考え、C1 と C2 を 1 pF とすると、80 MHz では 3978  $\Omega$ のインピーダンスが追加されるはずである。しかしながら、QMOD では[13]で示されたインピーダンス変換と同様の原理で、ノード A から RF 側を見た LO 周波数におけるインピーダンス(ZA)が周波数変換に伴って低周波の  $Z_{BBin}$  にダウンコンバートされてしまう。 $Z_{BBin}$  を大きくするには、LO 周波数近傍の ZA が大きくなるように設計する必要があった。加えて、[13]と異なり送信機の場合には、ノード B から BB 側を見た LO 周波数近傍のインピーダンス(ZB)も考慮する必要がある。なぜなら、BB バッファの出力インピーダンス(ZQ および ZQB)が LOQ と LOOB によってアップコンバートされて ZB となり ZA に影響するためである。

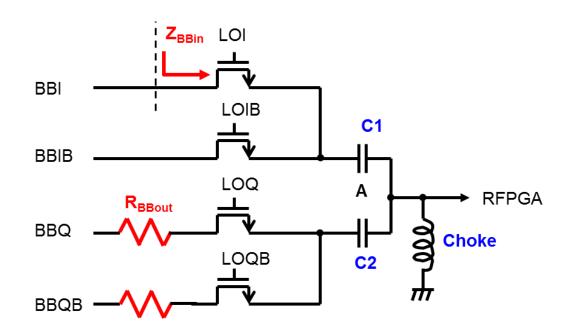

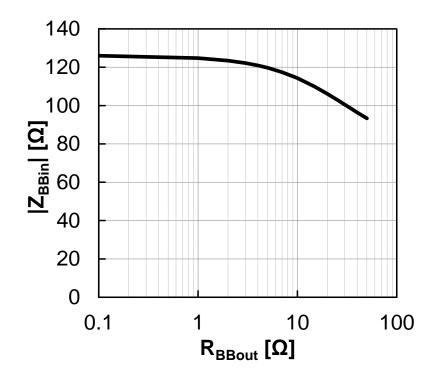

ZB の ZA への影響を明らかにするため、ノード A から RF 側を見た等価回路を図 3-9 に示す。ZA を増大させるため、チョーク・インダクタを用い、共振周波数を LO 周波数近傍に設定した。共振インピーダンスを最大化するには共振回路の Q 値を大きくする必要があり、ZQ (および ZQB) は低抵抗であるか、容量性のインピーダンスであることが求められる。DC 近傍の低周波で容量性のインピーダンスを実現することは困難であるため、BB バッファ回路の出力抵抗( $R_{BBout}$ )は低抵抗である必要がある。そこで、ソースフォロワ回路を BB バッファ回路として用いることとした。図 3-10 は、 $R_{BBout}$  の影響を調査するための回路であり、図 3-11 は図 3-10 の回路を用いてシミュレーションにより求めた  $Z_{BBin}$  の  $R_{BBout}$  依存性である。 $R_{BBout}$  が増加するに従って、 $Z_{BBin}$  は低下することが明らかとなった。しかしながら、ソースフォロワ回路の出力抵抗である 9  $\Omega$  の  $R_{BBout}$  では高い  $Z_{BBin}$  を保っており、114  $\Omega$  の  $Z_{BBin}$  となる見通しが得られた。図 3-7 に、提案した QMOD の  $Z_{BBin}$  も示した。提案した  $Z_{BBin}$  は 25% デューティ LO を用いた場合の約 1.5 倍である。これらの検討結果より、提案した QMOD は従来の QMOD に比べて高い線形性が得られるだけでなく、消費電力も低減できることが明らかとなった。

図 3-8 提案した QMOD 回路の構成

図 3-9 提案した QMOD 回路の等価回路

図 3-10 BB バッファの出力インピーダンスの影響を調べるための回路

図 3-11 BB バッファの出力インピーダンスの影響

#### 3.2.3 RF-PGA の設計

LTE 送信機において、利得可変機能は不可欠の機能である。図 3-12 は、設計した RF-PGA の回路構成である。RF-PGA は 10 個のユニット増幅器で構成され、それぞれが個別に制御される。ユニット増幅器は、ソース接地の差動増幅器と、差動カスコード増幅器からなる。ソース接地増幅器には、高利得が得られる 1.1 V 耐圧の MOS FET を、カスコード増幅器には耐圧超過による破壊を防ぐために 3.3 V の高耐圧 I/O 用 MOS FET を、それぞれ用いている。10 個のユニット増幅器のカスコード増幅器の出力はまとめられてバランに入力される。次節で示す通り、チップサイズをケアしながら RF-PGA のドレイン効率を最大化するため、入力インピーダンスと線路長を考慮してバランの設計を行った。

図 3-12 RF-PGA 回路の回路構成

#### 3.2.4 バランの設計

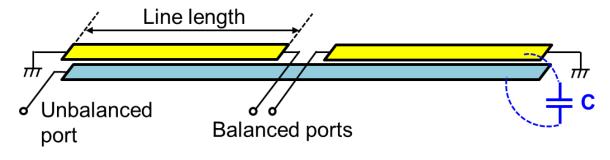

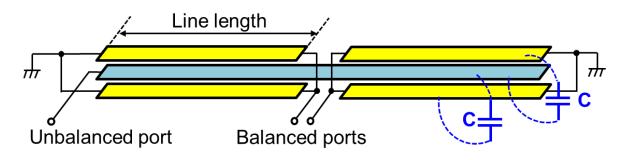

信号の波長に依存してしまうバランは、トランシーバにおいて広い面積を占有してしまうため、面積の低減が課題である。高い同相除去比 CMRR(Common-Mode Rejection Ratio)を得るため、トランスフォーマ型に比べて高い CMRR が得られるマーチャンド型バランを用いることとした。単純化したマーチャンド型バランの構造をに示す。従来のバランは、2層の配線層を用いて縦積み、または1層の配線層で並列に構成される。マーチャンド型バランの線路長は、以下の式で表わされる。

$$\theta \propto \frac{1}{\sqrt{L_{\nu}C_{\nu}}} \tag{3-1}$$

ここで、 $L_u$ および  $C_u$ は、それぞれ単位長さ当たりの線路のインダクタンスおよび容量である。式(3-1)は、線路長は  $L_u$  または  $C_u$  を増大することにより短縮できることを示している。

図 3-13 従来のバランの構造

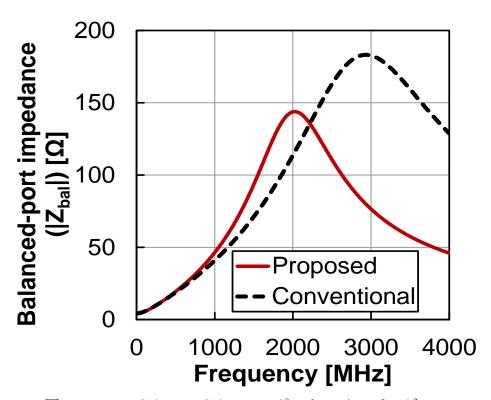

しかしながら、バランの設計には、バランの線路長だけでなく、RF-PGAのドレイン効率と耐圧の観点から、バランスポートの差動入力インピーダンスについても考慮しなければならない。図 3-12 に示すように、カスコード増幅器のゲートバイアス電圧は、ソース接地増幅器に用いられている 1.1 V 耐圧 MOS FET の耐圧を超過しないように、1.5 V の電圧が印加される。また、カスコード増幅器の 3.3 V MOS FET に関しても、耐圧のケアをする必要がある。本設計ではカスコード増幅用 FET (Q1、Q2)のソース電圧は 1.0 V であるため、ドレイン電圧は 4.3 V (ソース電圧+耐圧)以下にしなければならない。電源電圧は 2.8 V であるため、ドレインの電圧振幅に許容される最大値は 3.0 Vpp となる。一方で、RFIC は 0 dBm の送信信号を 50  $\Omega$ の負荷に供給しなければならない。8 dB の PAPR(Peak to Average Power Ratio)、3 dB のバランの損失、および 3 dB の設計余裕を考慮すると、最大で 14 dBm の信号

をバランのバランスポートに供給する必要がある。3.0 Vpp の電圧振幅で 14 dBm の信号電力を得るには、バランのバランスポートの入力インピーダンス( $|Z_{bal}|$ )は 179  $\Omega$ 以下に設定される必要がある。図 3-14 は、電磁界シミュレーションで求めた従来のマーチャンド型バランの $|Z_{bal}|$ である。 $|Z_{bal}|$ は最大で 180  $\Omega$ であった。以上より、バランの小型化検討にあたっては、 $|Z_{bal}|$ が増大しないように考慮して検討する必要があることが明らかとなった。

Z<sub>bal</sub> は、以下の式で表わされる[14]。

$$Z_{bal} = Z_{unb} \frac{1 - k^2}{k^2} \,, \tag{3-2}$$

ここで $Z_{unb}$ とkは、それぞれアンバランスポートに接続された回路の入力インピーダンス(ここでは即ち 50  $\Omega$ ) と結合伝送線路の結合係数である。式(3-2)より、k が増大すれば  $Z_{bal}$  が低下することがわかる。したがって、 $L_u$  または  $C_u$  の増加によって、k が増大することを示せれば、 $Z_{bal}$  も増大しないことが示される。結合係数 k は以下の式で表わされる。

$$k = \frac{Z_{oe} - Z_{oo}}{Z_{oe} + Z_{oo}},\tag{3-3}$$

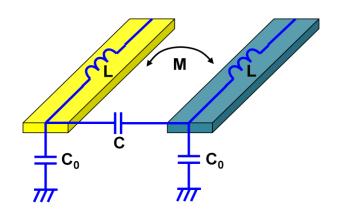

ここで  $\mathbf{Z}_{oe}$  と  $\mathbf{Z}_{oo}$  は、それぞれ結合伝送線路の偶モードインピーダンスと奇モードインピーダンスである。(3-3)式から、結合係数 k を増大するには、 $\mathbf{Z}_{oe}$  は増加、 $\mathbf{Z}_{oo}$  は減少する必要がある。図 3-15 は、簡略化した結合伝送線路の等価回路である。この等価回路から、 $\mathbf{Z}_{oe}$  と  $\mathbf{Z}_{oo}$  はそれぞれ以下の式で表わされる。

$$Z_{oe} = \sqrt{\frac{L+M}{C_0}},\tag{3-4}$$

$$Z_{oo} = \sqrt{\frac{L - M}{C_0 + 2C}},\tag{3-5}$$

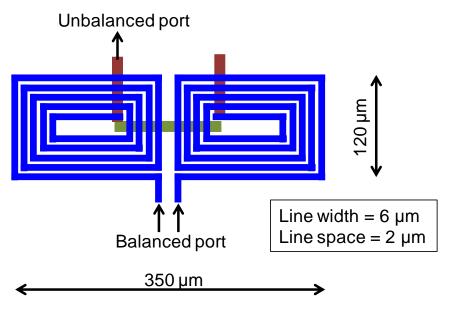

ここで、L、 $C_0$ 、M、C は、それぞれ伝送線路のインダクタンス、対接地容量、伝送線路間の相互インダクタンス、伝送線路間の容量である。ここで、 $Z_{oe}$ を増大させて  $Z_{oo}$ を低下させるには、M または C を増大させることで実現できる。しかしながら M の増加は伝送線路の単位長さ当たりのインダクタンス(即ち式(3-1)の  $L_{u}$ )を低下させてしまうため、マーチャンド型バランの線路長が長くなってしまう。一方、C の増加は伝送線路の  $C_{u}$  の増加と等価である。このことから、M が増大しないように C を増加することができれば、 $C_{bal}$  を増加させずにマーチャンド型バランの線路長を短縮することができることが分かる。そこで、図3-16 に示すような 3 層の配線層を用いたマーチャンド型バランを提案した。図 3-16 の構成を用いることで、結合伝送線路間の容量は従来に比べて約 2 倍にすることができる。一方、アンバランスポートが接続された 2 次側の線路のインダクタンスが低下するために M は 5%

程度低下する。しかしながらその低下量は、C が約 2 倍になったことと比較すると十分小さいため、マーチャンド型バランの線路長短縮と  $Z_{bal}$  の低下を同時に得ることができる。実際の配線構造を考慮すると、図 3-16 の最上層と中間層の間隔が  $0.74~\mu m$  であるのに対し、中間層と最下層の間隔は  $0.59~\mu m$  であるため、容量は 2 倍ではなく、正確には 2.25 倍となる。図 3-18 は、電磁界シミュレーション(Keysight Technologies 社製 ADS Momentum)により求めた、従来型の 2 層バランと提案したバランの伝達特性である。シミュレーションしたマーチャンド・バランの構成を図 3-17 に示す。総線路長は両方とも 1.8~m m にした。伝達特性がピークとなる周波数は、提案したバランの方が 2.0~GHz と従来のバランの 2.9~GHz に比べて 31%低くなっており、3~g 層構造を用いることでバランの線路長を短くできることが明らかとなった。図 3-14 には、提案したバランの  $Z_{bal}$  も示した。 $Z_{bal}$  は従来に比べて小さく、ピークでは  $142~\Omega$ となり、目標である  $179~\Omega$ 以下を達成できる見通しを得た。

図 3-14 バランのバランス・ポート・インピーダンス

図 3-15 結合伝送線路の等価回路

図 3-16 提案した 3 層マーチャンド型バランの構造

図 3-17 提案した 3 層マーチャンド型バランの構造

図 3-18 マーチャンド型バランの伝送特性

# 3.3 LTE 用送信機の測定結果

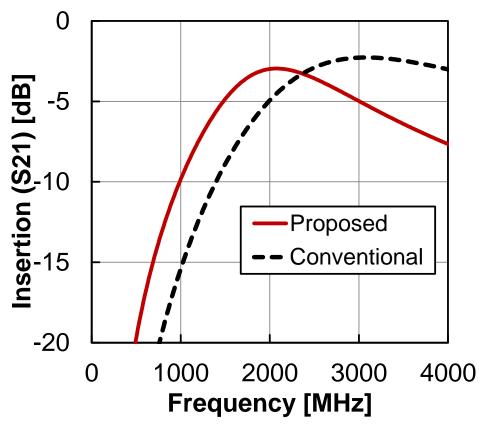

開発した LTE 用送信機のチップ写真を図 3-19 に示す。開発したチップは、TSMC 社の 65 nm CMOS プロセスを用いて試作した。チップサイズはボンディング・パッドを除くと 560  $\times$ 400  $\mu$ m である。QMOD は  $80\times200~\mu$ m であり、バランは  $120\times350~\mu$ m である。以降に示す全ての測定結果は、RF 出力ポートからの信号を測定して得られたものである。

図 3-19 開発した LTE バンド1 用送信回路のチップ写真

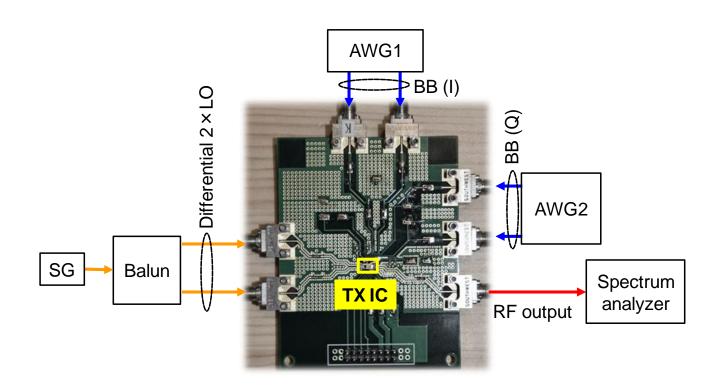

図 3-20 は、開発した送信機の測定系である。送信機 IC は実装評価基板に実装され、送信出力は基板に実装された RF コネクタから得られる。差動の LO 信号は、信号発生器 (Keysight Technologies 社製) により生成した LO 信号の 2 倍の周波数 (1950 MHz の RF であれば 3900 MHz) の信号を、オフチップのバランにより差動化されて入力される。BB 信号は任意波形発生器(Tektroniks 社製)を用いて生成し、I 信号と Q 信号の同期を取って入力した。送信出力は基板上に実装したマッチング回路 (今回はシリーズのコンデンサのみ)を介して出力される。

図 3-20 開発した LTE バンド 1 用送信回路の測定系

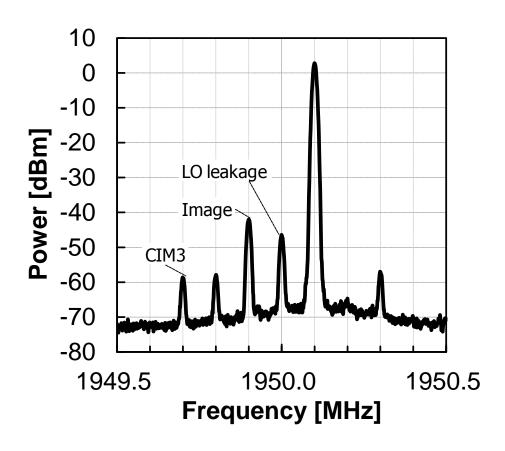

図 3-21 は、送信機の出力スペクトラムである。RFPGA のコードを最大に(=10)して送信出力を 1.8 dBm に設定している。入力した信号設定は以下のとおりである。 $2\times LO$  信号は、周波数を 3900 MHz、信号電力を 10 dBm に設定した。バランの損失を 1 dB とすると、差動それぞれで 6 dBm の信号となる。BB 信号は 100 kHz の CW 信号とした。振幅は、最大振幅を 1.0 Vpp とし 8 dB のバックオフを想定して、400 mVpp の振幅で入力している。以上の設定より、所望波は周波数が 1950.1 MHz となる。ダイレクト・コンバージョン形式の送信ミキサでは、所望波以外の不要波(特に、LO 漏洩電力、イメージ信号、カウンターIM3(CIM3)信号)の評価が必要である。不要波が大きいと、送信信号の EVM(Error Vector Magnitude)が劣化したり、隣接チャネル漏洩電力が増大したりして、通信品質が劣化する問題を引き起こしてしまう。LO 漏洩電力は、固定周波数である LO 信号が周波数変換されずにそのまま出力される成分である。イメージ信号、CIM3 は、LO を対称として所望波の逆の周波数に発生する成分であり、それぞれ 1 倍、3 倍の周波数に発生する。LO 漏洩電力、イメージ信号、CIM3 信号は、それぞれ-49.2 dBc、-44.8 dBc、-61.5 dBc と良好な値を示している。

図 3-21 開発した LTE バンド 1 用送信回路の出力スペクトラム

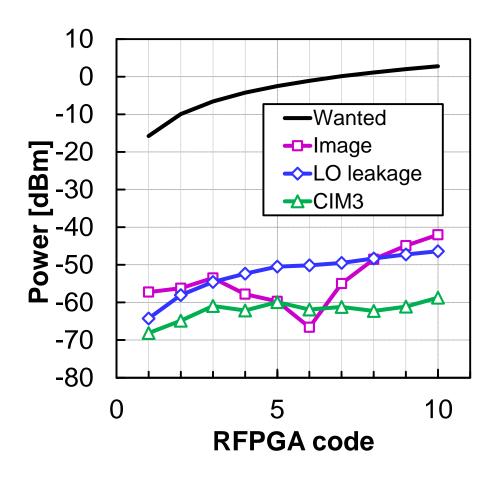

図 3-22 は、送信電力、LO 漏洩電力、イメージ信号電力、CIM3 信号電力の RFPGA コード依存性を示している。送信電力は 20 dB の制御範囲を得ており、最小電力は-18 dBm である。また、全ての不要信号は、全 RFPGA コードに渡って-40 dBm 以下に抑圧されている。

図 3-22 開発した LTE バンド 1 用送信回路の出力電力と不要波の RF-PGA コード依存性

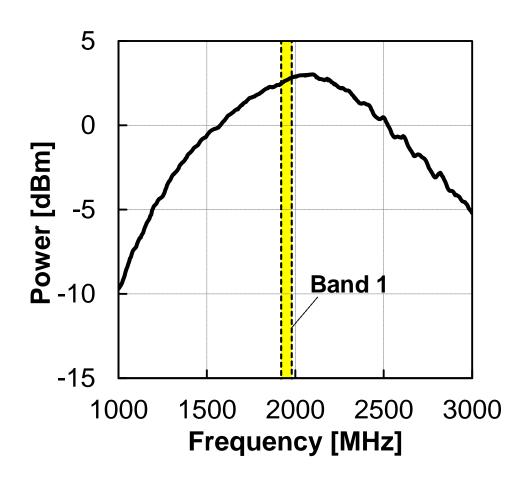

図 3-23 は、LO 周波数に対する送信出力電力の依存性である。図 3-23 の特性は、 $2\times LO$  信号の周波数を掃引して測定した。BB 信号は周波数 100~kHz、振幅 400~mVpp の CW 信号とした。ピーク電力を示す周波数は 2070~MHz であり、バンド 1~o中心周波数(1950~MHz)からは 120~MHz ずれているが、バンド 1~o帯域においてもピークから 1~dB 以内の低下に収まっており、実用上問題ない。

図 3-23 開発した LTE バンド 1 用送信回路の出力電力の LO 周波数依存性

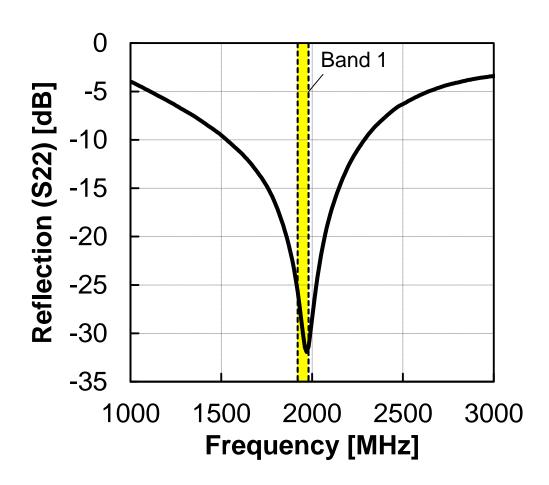

図 3-24 は送信出力の反射特性である。反射特性は、LO 信号を入力しない状態で、RFPGA コードを最大にして測定した。バンド 1 の帯域内では-25 dB 以下と良好な反射特性が得られた。図 3-23 および図 3-24 の測定結果から、チョーク・インダクタやマーチャンド型バランがほぼ設計通りに作製されていると判断できる。

図 3-24 開発した LTE バンド1 用送信回路の出力反射特性

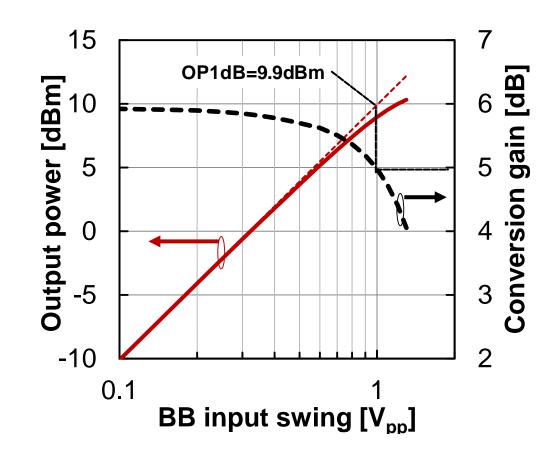

図 3-25 は、BB 入力電圧振幅に対する送信出力電力の依存性である。出力電力は赤の実線で、変換利得は破線で示した。振幅変調を伴う高次の変調システムにおける送信機の重要な歪み特性である出力 1 dB 利得圧縮点(Output Point of 1dB gain compression)は、理想的な直線の利得特性に対して、1 dB 低下した点の出力電力である。図 3-25 から、開発した送信機のOP1dB は 9.9 dBm であった。このことから、LTE の変調に必要な 8 dB のバックオフを確保すると、1.9 dBm が最大の平均出力電力となる。これは、他の報告例 [4,5,7] と比べても遜色ない良好な特性であり、提案した QMOD と RFPGA(バランを含む)の構成によるものである。

図 3-25 開発した LTE バンド 1 用送信回路の入出力特性

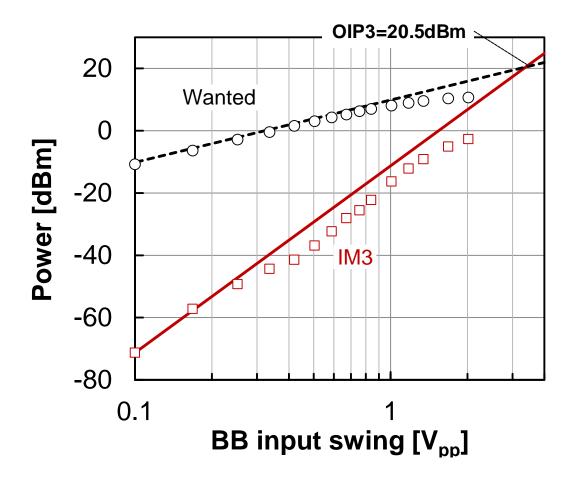

図 3-26 は、2トーン測定結果である。出力 3 次インターセプト・ポイント ( $\underline{O}$ utput  $3^{rd}$ -order Intercept Point) は、OP1dB と並んで重要な歪み特性である。OP1dB が歪み特性を利得の低下として観測するのに対して、OIP3 は 3 次歪み量を観測して得られ、3 次歪み量が所望波と同等になる出力電力である。本開発の送信機の OIP3 は 20.5 dBm であった。これは、他の報告例 [4,5,7] と比べても遜色ない良好な特性であり、提案した QMOD(容量を用いた IQ合成技術)と RFPGA(バランの入力インピーダンスの最適化)の構成によるものである。

図 3-26 開発した LTE バンド1 用送信回路の3 次歪み測定結果

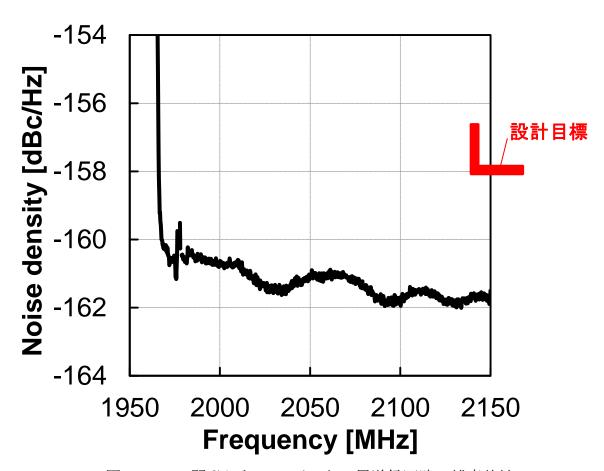

図 3-27 は、バンド外雑音の測定結果である。送信電力は 1.8 dBm である。図 3-27 は、スペクトラム・アナライザで測定したのであるが、送信電力が大きくスペクトラム・アナライザのダイナミック・レンジが不足して雑音を正確に測定できない問題があった。そこで、送信電力をノッチフィルタで減衰させて、さらに低雑音の増幅器で増幅して測定した。バンド1の受信帯域(190 MHz 離調)では、雑音密度は-161.6 dBc/Hz であり、LTE 送信機としては十分に低い雑音を達成することができた。

図 3-27 開発した LTE バンド 1 用送信回路の雑音特性

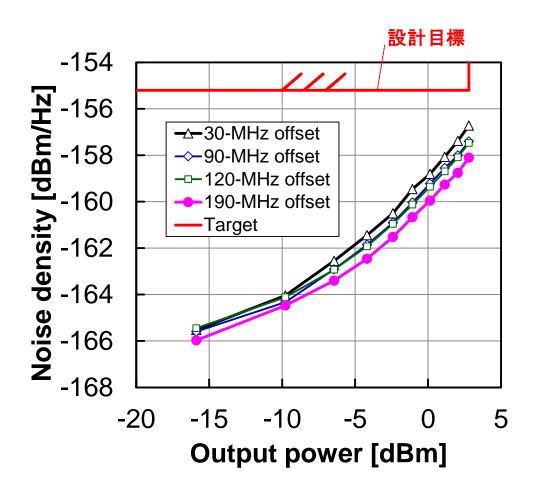

バンド1は受信帯域が190 MHz 離調であるが、受信帯域はバンドによって離調周波数が異なる。例えばバンド2では95 MHzであり、バンド14に至ってはわずか30 MHzしか離れていない。そこで、バンド1以外への本技術の適用可能性を判断するため、190 MHz以外の代表的な離調周波数(30 MHz、90 MHz、120 MHz、190 MHz)における雑音電力密度の測定結果を図3-28にまとめた。送信電力の制御は、RFPGAコードを調整して行った。全ての送信電力範囲、および各離調周波数において、-156.2 dBm/Hz以下の雑音電力を達成しており、バンド1だけでなくその他のバンドへの適用も可能であることが示された。

図 3-28 開発した LTE バンド 1 用送信回路の雑音特性

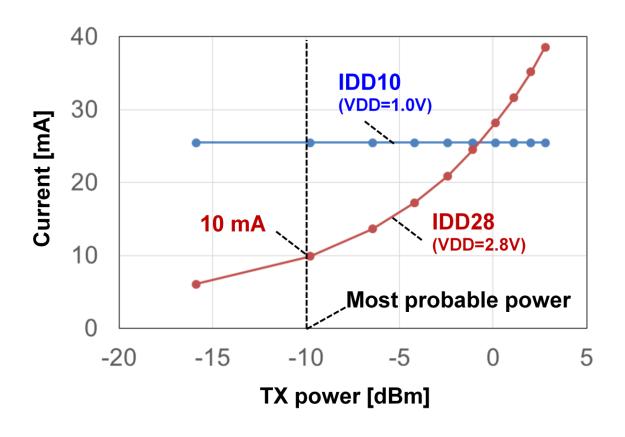

図 3-29 は、測定した消費電流の送信電力に対する依存性である。送信電力の制御は、RFPGA コードを調整して行った。1.0 V電源の消費電流は、RFPGA コードを調整しても影響はなく、送信電力に対して一定で常に25.5 mAである。RFPGA コードを増やして送信電力を増大するに従って、RFPGA の電源である2.8 V電源の消費電流は増加し、最大で39 mAとなる。最大電流は重要な性能指標であるが、LTE 送信機においては、実際のモバイル端末の使用条件における消費電流も重要となる。モバイル端末において、最も高確率で設定される送信電力は-10 dBm 前後であり、その時の消費電流が重要な性能指標となる。開発した送信機では10 mAであった。

図 3-29 開発した LTE バンド 1 用送信回路の消費電流

以上の測定結果のベンチマーク結果を表 3-1 に示す。開発した送信機は、高い線形性と十分に低い受信帯域雑音を達成しているだけでなく、表の中では最も小さいチップサイズを実現している。また、比較的古いプロセスを使用しているにもかかわらず、消費電力は BB バッファを搭載した他の報告例に比べても遜色ない結果となり、提案した QMOD 回路の有効性が示された。

表 3-1 性能比較

| Item                                 |           | Unit   | X. He, et al.                                           | J. Craninckx, et al.                        | T. Kihara, et al.           | This work                                                     |  |

|--------------------------------------|-----------|--------|---------------------------------------------------------|---------------------------------------------|-----------------------------|---------------------------------------------------------------|--|

| Carrier                              |           | MHz    | 1950 1950 700-2600                                      |                                             | 700-2600                    | 1950                                                          |  |

| Process                              |           | nm     | 45                                                      | 40                                          | 65                          | 65                                                            |  |

| Pout                                 |           | dBm    | +1/+4 2.1 2.1                                           |                                             | 2.8                         |                                                               |  |

| OP1dB                                |           | dBm    | NA                                                      | 10.4                                        | NA                          | 9.9                                                           |  |

| OIP3                                 |           | dBm    | 24                                                      | NA                                          | NA                          | 20.5                                                          |  |

| Rx-band noise                        |           | dBc/Hz | -159                                                    | -160                                        | -161                        | -161                                                          |  |

| Power consumption<br>/Supply voltage |           | mA     | 6.05mW/1.1V (LO)<br>NA (BB buffer)<br>20.3mW/1.8V (PPA) | 27.5mW/1.1V<br>(LO+LPF)<br>100mW/2.5V (PPA) | 32.4mW/1.2V<br>123.2mW/2.8V | 25.5mW/1.0V<br>(Divider+BB buffer)<br>108.0mW/2.8V<br>(RFPGA) |  |

| Integration                          | BB buffer | -      | No                                                      | Yes                                         |                             | Yes                                                           |  |

|                                      | Divider   | -      | Yes                                                     | Yes                                         |                             | Yes                                                           |  |

|                                      | QMOD      | -      | Yes                                                     | Yes                                         | Fully-integrated            | Yes                                                           |  |

|                                      | RFPGA     | _      | Yes                                                     | Yes                                         |                             | Yes                                                           |  |

|                                      | PLL       | _      | No                                                      | No                                          |                             | No                                                            |  |

# 3.4 **まとめ**

65 nm CMOS プロセスを用いて LTE バンド 1 用の SAW レス送信機のプロトタイプを開発した。開発した送信機の設計においては、低雑音特性と高線形性を実現し、かつフルバンド対応には不可欠な奇数分周によって得られる局部発振信号にも対応できるように、容量を介して In-phase 信号と Quadrature 信号を合成する受動型の直交変調器を提案した。また、RF-PGA のドレイン効率と耐圧を考慮して入力インピーダンスを増加せずに配線長を短縮できる 3 層構造のマーチャンド型バランを提案した。これらの技術を適用することで、開発した送信機は、低い受信帯域雑音(<-161.6 dBc/Hz)と高い線形性(OIP3 = 20.5 dBm)を、0.224 mm² の占有面積で実現した。

### 参考文献

- [1] K. Ueda, T. Uozumi, R. Endo, T. Nakamura, T. Heima, and H. Sato, "A Digital PLL with Two-step Closed-locking for Multi-mode/Multi-band SAW-less Transmitter," in *Proc. of IEEE Custom Integrated Circuits Conf.*, September, 2012, pp. 1-4.

- [2] M. Farazian, B. Asuri, and L. E. Larson, "A Dual-Band CMOS CDMA Transmitter Without External SAW Filtering," *IEEE Trans. Microwave Theory and Techniques*, vol. 58, no. 5, pp. 1349-1358, May, 2010.

- [3] T. Sowlati, *et al.*, "Single-Chip Multiband WCDMA/HSDPA/HSUPA/EGPRS Transceiver with Diversity Receiver and 3G DigRF Interface Without SAW Filters in Transmitter / 3G Receiver Paths," in *IEEE Int. Solid-State Circuits Conf. Dig.*, Feb. 2009, pp. 116-117.

- [4] J. Craninckx, J. Borremans, and M. Ingels, "SAW-less Software-Defined Radio Transceivers in 40nm CMOS," in *Proc. of IEEE Custom Integrated Circuits Conf.*, September, 2011, pp. 1-8.

- [5] T. Kihara, T. Sano, M. Mizokami, Y. Furuta, T. Nakamura, M. Hokazono, T. Maruyama, K. Toyota, K. Maeda, Y. Akamine, T. Yamawaki, T. Heima, K. Hori, and H. Sato "A Multiband LTE SAW-Less CMOS Transmitter with Source-Follower-Driven Passive Mixers, Envelope-Tracked RF-PGAs, and Marchand Baluns", in *IEEE Radio Frequency Integrated Circuits Symp. Dig.*, pp. 399-402, June 2012.

- [6] S. D'Souza, F. Chang, S. Pamarti, B. Agarwal, H. Zarei, T. Sowlati, and R. Berenguer, "A Progammable Baseband Anti-Alias Filter for a Passive-Mixer-Based, SAW-less, Multi-Band, Multi-Mode WEDGE Transmitter," in *IEEE Int. Symp. on Circuits and Systems Dig.*, May 2011, pp.450-453.

- [7] X. He and J. van Sinderen, "A Low-Power, Low-EVM, SAW-Less WCDMA Transmitter Using Direct Quadrature Voltage Modulation," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3448-3458, December 2009.

- [8] V. Giannini, M. Ingels, T. Sano, B. Debaillie, J. Borremans, and J. Craninckx, "A Multiband LTE SAW-less Modulator with -160dBc/Hz RX-Band Noise in 40nm LP CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig.*, Feb. 2011, pp. 374-375.

- [9] M. Ingels, Y. Furuta, X. Zhang, S. Cha, and J. Craninckx, "A Multiband 40nm CMOS LTE SAW-Less Modulator with -60dBc C-IM3," in *IEEE Int. Solid-State Circuits Conf. Dig.*, Feb. 2013, pp. 338-339.

- [10] H. Kamizuma, et al., "A quad band WCDMA transceiver with fractional local divider," in *IEEE Symposium on VLSI Circuits.*, pp. 96-97, June 2008.

- [11] S.-C. Tseng, *et al.*, "Monolithic Broadband Gilbert Micromixer With an Integrated Marchand Balun Using Standard Silicon IC Process," *IEEE Trans. Microwave Theory and Techniques*, vol. 54, no. 12, pp. 4362-4371, December 2006.

- [12] T.-G. Ma, *et al.*, "Miniaturized Distributed Marchand Balun Using Coupled Synthesized CPWs," in *IEEE Microwave and Wireless Components Letters*, vol. 21, no. 4, pp. 188-190, April 2011.

- [13] A. Mirzaei, H. Darabi, A. Yazdi, Z. Zhou, E. Chang, and P. Suri, "A 65 nm CMOS Quad-Band SAW-Less Receiver SoC for GSM/GPRS/EDGE," *IEEE J. Solid-State Circuits*, vol. 46, no. 4, pp. 950-964, April 2011.

- [14] W.J. Feng and W.Q. Che, "Ultra-wideband bandpass filter using broadband planar Marchand balun," in *IEEE Electronics Letters*, vol. 47, no. 3, pp. xx, February, 2011.

- [15] O. Olieri, et al., "A multiband multimode transmitter without driver amplifier," in *IEEE Int. Solid-State Circuits Conf. Dig.*, Feb. 2012, pp. 164-165.

第4章 周波数シンセサイザの低消費電力化技術

## 4.1 背景

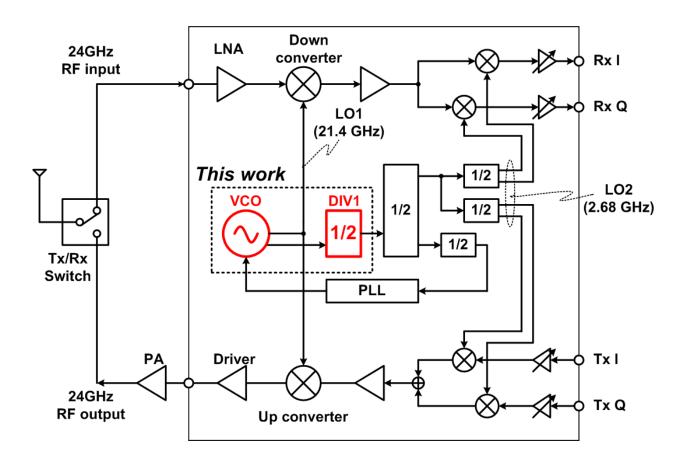

モバイル機器の高機能化に伴って、各モジュールの消費電力低減が求められており、通信モジュールも同様である。図 4-1 は一般的なスライディング IF 形式の通信モジュールの構成である。特に消費電力が大きいのはパワーアンプであるが、RFIC の構成ブロックでは、ドライバ回路(Driver)と周波数シンセサイザの消費電力が大きい。周波数シンセサイザの構成ブロックでは、電圧制御発振回路(VCO)とプリスケーラ(初段の分周回路)の消費電力が大きい。そのため、VCO とプリスケーラについて、消費電力低減のために検討した技術について述べる。本章では 24 GHz 帯のトランシーバ向けに開発した技術について述べるが、検討および提案した低消費電力化に関する技術は、10 GHz 以下のマイクロ波帯でも用いることが可能である。

ライセンスフリーの ISM (Industrial, Scientific and Medical) バンドである 24 GHz 帯を用い た、図 4-1 のスライディング IF 形式のトランシーバについて説明する。周波数シンセサイ ザは、1/8 の周波数を第 2 の LO (LO2) として用いることから、21.4 GHz (≒24.125 GHz× 8/9) を VCO の発振周波数に設定した。シリコンプロセスの高度化によって、このような高 い周波数においても低コストのシリコンプロセスを用いたトランシーバの開発が進められ ている[1,2]が、依然として消費電力が高い問題があった。図 4-1 に示す構成ブロックのうち で、ダウンコンバータ[3]やイメージ抑圧 LNA(Low Noise Amplifier)[4]は既にシリコンプ ロセスを用いて低消費電力で実現されている。しかしながら、周波数シンセサイザに関して は、十分に低い消費電力で必要な性能を実現するには至っていない。周波数シンセサイザに おいて消費電力の大きいブロックは、上述したようにVCOと分周器である。VCOの機能は、 高次の位相変調通信システムにおいて重要な特性である位相雑音の低い局部発振信号を供 給することにある。低電圧動作の CMOS プロセスを用いて低位相雑音と低消費電力を実現 した VCO は多く報告さている[5-9]が、プロセスばらつきや電源・温度変動(総合して PVT (Process, Voltage, and Temperature) ばらつき)を考慮すると、周波数可変範囲が十分ではな い。このような変動に対応するためには、事前検討によれば12%以上の周波数可変範囲が余 分に必要である。また、電源電圧に対する周波数変動を抑圧するには、レギュレータを用い ることが有効である。

周波数分周器に関しては、低消費電力化の一つの方策はインジェクション・ロック分周器(Injection Locked Frequency Divider)[5,10]の使用である。しかしながら、ILFD は負荷回路にインダクタを用いるため、周波数範囲が狭い問題や、チップサイズが大きくなる問題が発生する。狭い周波数範囲は、VCO の自動周波数バンド補正[11]を実施する際に問題となる。上述したように、VCO の周波数は PVT ばらつきで 12%以上変動するため、分周器は VCO の周波数可変範囲(本設計では 20%)に加えて 12%の周波数範囲(合計で 32%の周波数範囲)で動作する必要がある。インダクタ負荷の ILFD 以外の分周器としては、通常のマスタ

ー/スレーブ・フリップフロップ回路を用いたスタティック分周器や、リング発振器をベースにした ILFD[12]やダイナミック分周器[13]が挙げられるが、消費電力が大きい問題がある。

図 4-1 24GHz 帯スライディング IF 形式のトランシーバ構成

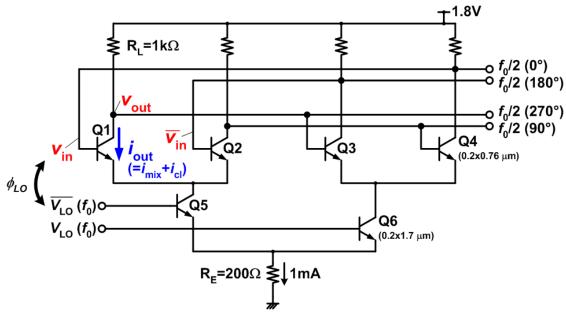

# 4.2 回路設計

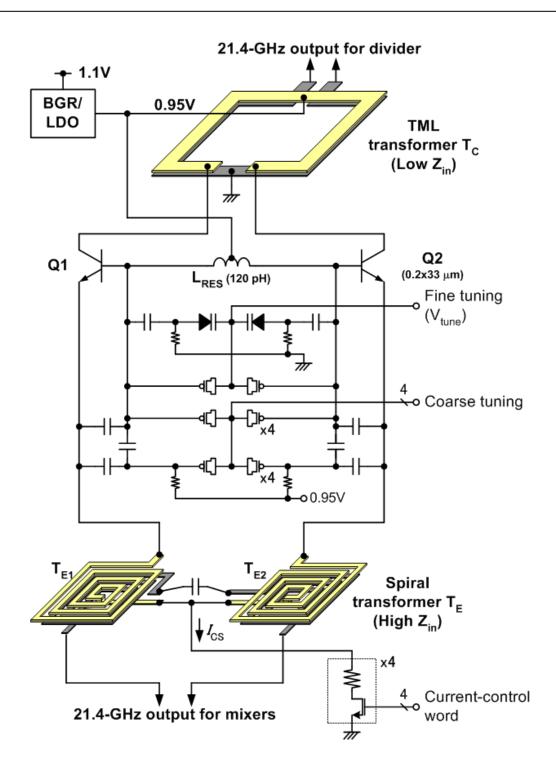

図 4-1 に、開発した 21.4 GHz 動作の周波数シンセサイザのブロック構成を示す。開発した周波数シンセサイザは、21.4 GHz の第 1 の LO(LO1)と 2.68 GHz の第 2 の LO(LO2)を供給する。シンセサイザは、VCO、初段分周器(DIV1)、LO2 用の分周器群と PLL 用のブロックで構成される。DIV1 以外の分周器は、スタティック分周器で構成される。これらの回路は、SiGe BiCMOS プロセス[14, 15]( $f_{\rm T}/f_{\rm max}$  = 150/200 GHz、Al 配線最上層膜厚=3  $\mu$ m)を用いて設計・試作した。

図 4-2 提案した VCO の構成

#### 4.2.1 VCO の設計

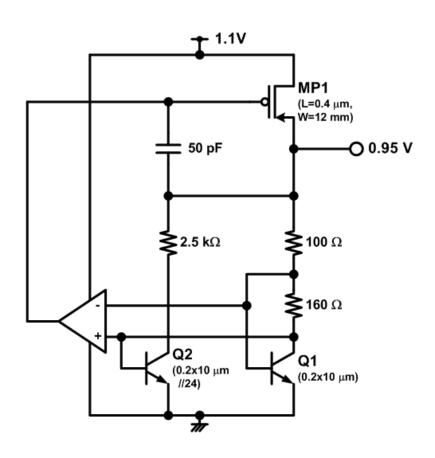

提案した VCO の回路構成を図 4-2 に示す。電源電圧は、BGR(Band-Gap Reference)を備えた LDO(Low-Drop Out)から供給される。LDO の回路構成は図 4-3 に示した。LDO の回路トポロジーは、Self-Regulating VCO[16]で用いられている LDO を参考にした。LDO は 0.95 V の電圧を VCO に供給し、LDO 自身は 2.8 mW の DC 電力を消費する。VCO の回路トポロジーは、波形の歪みを低減できるために低位相雑音特性が実現できる差動コルピッツ形式[17-19]を採用した。共振回路は、インダクタ(LRES~110 pH)、粗調整用の 2 つの 4 ビット MOS バラクタ容量バンク、高線形の微調整用の MOS バラクタ容量と pn ジャンクション容量で構成される。大きな信号強度の LO1 をミキサ回路に供給するため、再利用トランスフォーマ(図 4-2 中の TE)出力技術[18]を用いた。この技術を用いることで、バッファ回路なしに、ミキサ回路を駆動することができる。この回路トポロジーを採用するために、RFと LO1 間のアイソレーション、特に RF 信号の初段分周器への漏洩に関して確認する必要があった。

図 4-3 LDO の回路構成

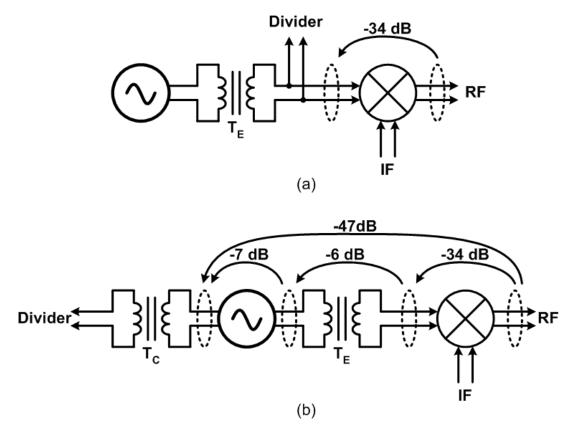

まず、再利用トランスフォーマ技術を用いて送信ミキサと初段分周器の両方を駆動する構 成(図 4-4(a)) について考察する。この場合、ミキサにおける RF から LO1 に漏洩した信号 は、直接分周器に入力される。電磁界シミュレーション (Keysight Technologies 社製 ADS Momentum) 結果から漏洩量を見積もったところ、-34 dBc の RF 信号が LO1 に漏洩するこ とが分かった。RF 信号が DIV1 に入力されると、RF と LO1 の差分が LO2 の周波数である ため、RFとLO1の混変調によりLO2近傍にTX信号が重畳された信号が発生する。この信 号がLO2に重畳されるため、BB信号の2次変調が発生してしまい、送受信信号のEVM(Error Vector Magnitude)が悪化する問題が発生することが予測された。そのため、DIV1入力とミ キサの LO1 入力は十分にアイソレートされる必要があることがある。信号の分離のために はバッファ回路を用いることが従来の解決方法であるが、バッファ回路による消費電力を削 減するため、新たなトランスフォーマ(TC)を図 4-2 の VCO の Q1 および Q2 のコレクタ に追加し、このトランスフォーマの出力を DIV1 の入力とする構成を提案した。このような 構成を採用することで、図 4-4(b)に示すように、TE および TC の損失、Q1 および Q2 のエ ミッタからコレクタへのアイソレーションが RF と DIV1 入力間のアイソレーションに追加 され、アイソレーションが向上される。図 4-4(b)に示すように、従来の構成に比べて 13 dB 大きなアイソレーションを実現できる見通しである。

図 4-4 RF と分周器入力のアイソレーション比較

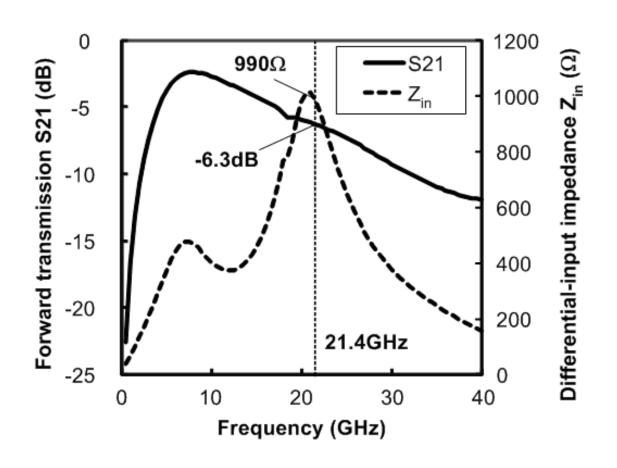

トランスフォーマ TE および TC は、VCO の特性を悪化させないように VCO の特性への影響を考慮して設計した。図 4-2 の Q1 および Q2 のエミッタに接続される TE は、大きな負性コンダクタンスを得るために、入力インピーダンスを高くする必要がある。そこで、TE の 1 次側インダクタ (LPRI) には、スパイラル・インダクタを用いた。2 次側インダクタ (LSEC) は、大きな相互インダクタンスを得るためとサイズ低減を目的に、LPRI の下層配線で構成した。電磁界シミュレーション(Keysight Technologies 社製 ADS Momentum)を用いて求めた伝達特性(S21)と入力インピーダンスを図 4-5 に示す。21.4 GHz では、損失は 6.3 dB であり、入力インピーダンスは 990  $\Omega$  と高く設計することができた。

図 4-5 TE の伝達特性と入力インピーダンスのシミュレーション結果

一方、TC は、ミラー効果によるベース・コレクタ間の寄生容量の影響増大を防ぐため、 入力インピーダンスを低くする必要がある。そこで、線幅が 20 μm と太い結合伝送線路を用いたトランスフォーマを用い、さらに、容量性のインピーダンスとなる領域で用いる構成を 提案した。結合伝送線路を用いたトランスフォーマは、サイズが大きくなることが懸念され るが、DIV1 の入力インピーダンスが 500 Ω程度と大きいために 2 次側線路に大きなリターン電流が流れないことから、通常の伝送線路と比べて波長を短くすることができる。そのため、容量性の入力インピーダンスに見せるための線路長も短くできる。1 次側と 2 次側の線路は、それぞれ最上層 (M6) の配線とその 1 層下 (M5) の配線で構成した。

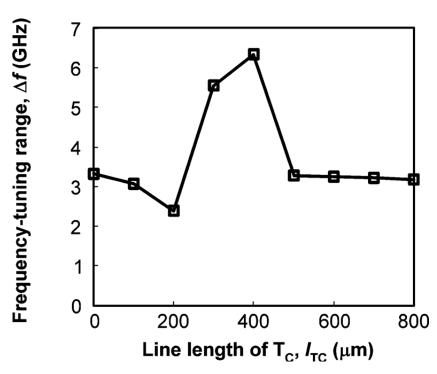

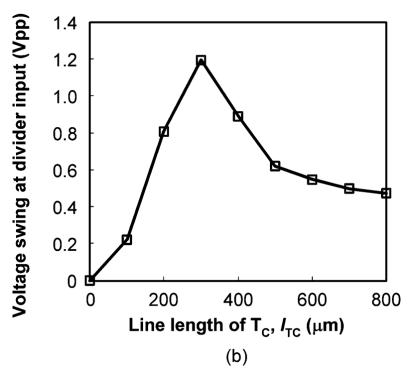

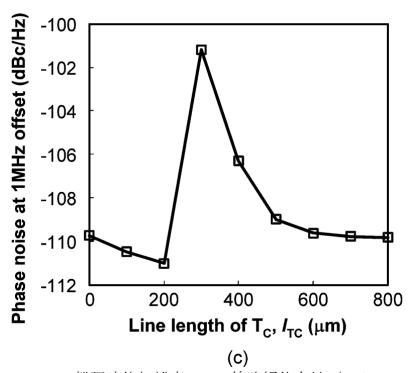

TC の配線長を最適化するため、VCO の周波数可変範囲、DIV1 入力の電圧振幅、21.4 GHz 信号の 1MHz 離調時の位相雑音の TC の線路長 ( $I_{TC}$ ) 依存性をシミュレーションにより求め、それぞれ図 4-6 (a)~(c)に示した。ここでは、周波数可変範囲は周波数粗調整による可変範囲のみであり、微調整分の可変範囲は含まれていない。入力インピーダンスが誘導性である領域(すなわち  $I_{TC}$  < 300  $\mu$ m)では、位相雑音は  $I_{TC}$  がゼロの時に比べて改善するが、ミラー効果によって周波数可変範囲が狭くなる。TC の共振周波数が 21.4 GHz 近傍になる  $I_{TC}$  が 300  $\mu$ m 近傍では、電圧振幅と周波数可変範囲は増加/拡大するが、位相雑音が大幅に悪化してしまう。 TC の入力インピーダンスが容量性となる  $I_{TC}$  が 600  $\mu$ m 以上の領域では、全ての特性がマージナルとなる。以上の検討結果から、TC には 600  $\mu$ m の長さの結合伝送線路型トランスフォーマを用いることとした。電磁界シミュレーションにより求めた TC の伝達特性(S21)と入力インピーダンスを図 4-7 に示す。21.4 GHz では、損失は 6.5 dB であり、差動の入力インピーダンスの絶対値は 39.0  $\Omega$  と低く、またインピーダンスの位相は-74.5°と容量性に設計することができた。また、ミラー効果による実効容量の増大は、抵抗性のインピーダンスのみが影響するため、抵抗性のインピーダンスも求めたところ、10.4  $\Omega$  と非常に低く設計することができた。

図 4-6(a) VCO の周波数可変範囲の TC 線路帳依存性(シミュレーション結果)

図 4.6 (b) VCO の DIV 出力の電圧振幅の TC 線路帳依存性 (シミュレーション結果)

図 4.6 (c) VCO の 1 MHz 離調時位相雑音の TC 線路帳依存性 (シミュレーション結果)

図 4-7 TC の伝達特性 (a) と入力インピーダンス (b)

## 4.2.2 周波数分周器 (DIV1) の設計

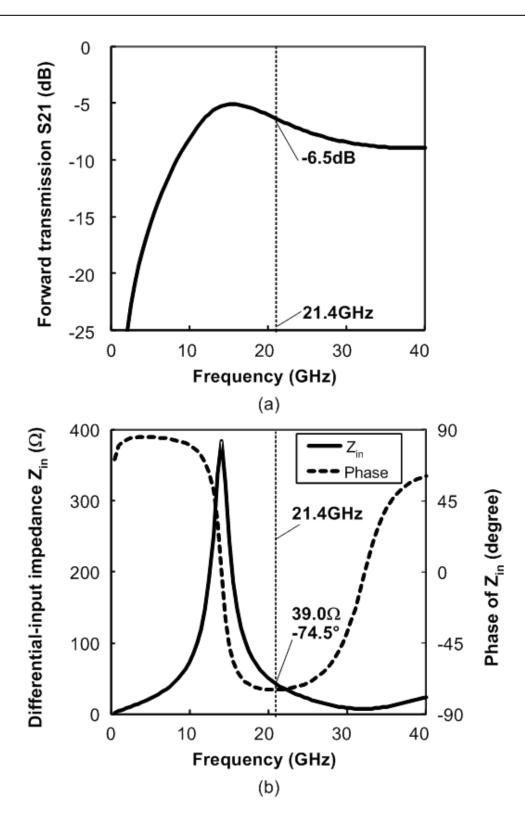

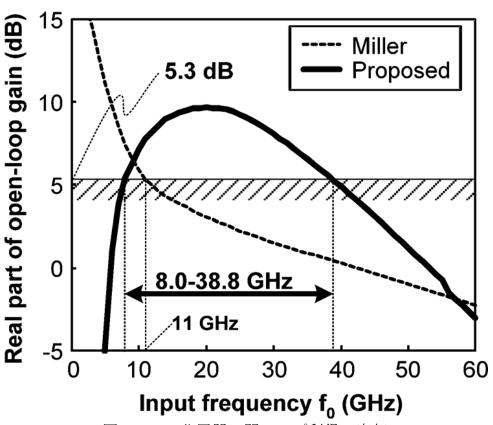

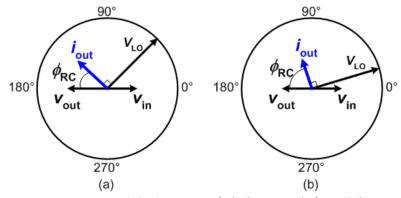

ダイナミック分周器は、低消費電力化に有効な選択であるが、従来の分周器は、広い周波 数範囲と低消費電力を両立することが困難であった。ダイナミック分周器の一種であるダブ ル・バランス・ミキサをベースにしたミラー分周器の従来回路構成を図 4-8 に示す。分周動 作範囲を確認するため、開ループ利得をシミュレーションにより求めた。図 4-9 に、 $\nu_{in}$  か ら  $v_{\text{out}}$  の開ループ利得の実部を点線で示した。横軸は分周器の入力周波数であり、図 4-9 に 示した開ループ利得は、半分の周波数で求めたものである。ループ利息は、ミキサの変換利 得に依存し、周波数の増加とともに減少する。分周器動作を行うためには、ループ利得が 0dB 以上であることが必要条件である。図 4-9 に示す通り、21.4 GHz では 2.8 dB であり、 必要条件を満たしている。しかしながら、シミュレーションでは、理想的なバッファ回路(入 力抵抗/出力抵抗= $1 M\Omega / 1 m\Omega$ )を用いた場合でも、最大動作周波数は11 GHzであった。 11 GHz における開ループ利得は 5.3 dB であることから、5.3 dB の開ループ利得が分周動作 を開始するための十分条件であると判断した。図 4-8 の従来回路を用いて周波数範囲を拡大 するには、消費電流を大きくしたりインダクタを用いたりしてループ利得を増大させる必要 がある。そこで、2つのシングル・バランス・ミキサを用いた疑似スタティックのダイナミ ック分周器(図 4-10)を提案した。シングル・バランス・ミキサはキャリア・リークが大 きいため変調器や復調器に用いるには問題があるが、分周器においてはキャリア・リークに よって利得を増大させることが可能となり低消費電力化に有効である。

図 4-8 従来のミラー型ダイナミック分周器

図 4-9 分周器の開ループ利得の実部

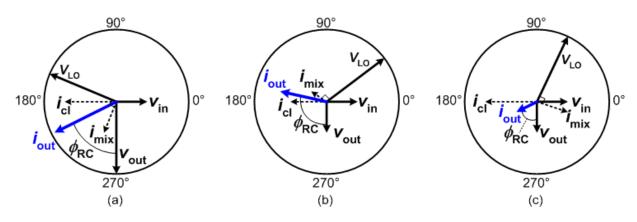

提案した分周器の従来例に対する利点を図 4-11 および図 4-12 を用いて説明する。従来のミラー分周器の分周動作時における入力および出力電圧信号、入力 LO 信号、および出力電流信号の振幅と位相を図 4-11 に模式的に示した。図 4-8 において  $\phi_{RC}$  は負荷回路(抵抗RL と寄生容量)によって生成される位相シフト量である。出力電流は  $f_0$  信号と  $f_0/2$  信号のミキシングにより生成されるため、出力電流の位相は  $f_0$  信号の位相( $\phi_{LO}$ )で決定され、 $\phi_{LO}$  +  $90^\circ$  となる。分周動作を実現するには、出力電圧信号の位相は入力電圧信号から  $180^\circ$  シフトされる必要がある。この位相シフトは、 $f_0$  と  $f_0/2$  の信号の位相差が最適な位相差になるように収束することで達成される。しかしながら、図 4-11 に示すように、周波数が高くなるにつれて変換利得は低下すだけでなく負荷回路による損失も増大するため、出力電流は低下する。結果として、ループ利得が低下し、分周動作が達成できなくなる。

図 4-10 提案した分周器の回路構成

図 4-11 従来分周器の内部信号の強度と位相

図 4-12 提案した分周器の内部信号の強度と位相

図 4-12 に、提案した分周器を構成する初段のシングル・バランス・ミキサにおける入出 力電圧信号( $v_{\rm in}/v_{

m out}$ )、LO 電圧信号( $v_{

m LO}$ )、出力電流信号( $i_{

m out}$ )の振幅と位相を模式的に表 わした。分周動作を実現するためには、提案した分周器のミキサ回路によって、270°の位 相シフトが必要となる。シングル・バランス・ミキサはダブル・バランス・ミキサと異なり、 キャリア・リーク信号  $(i_{cl})$  とミキシング信号  $(i_{mix})$  の 2 種の電流信号を出力する。 $i_{cl}$  の位 相は、入力電圧信号の逆位相となる。上述した従来の分周器と同様の仕組みで、imix の位相 は出力電圧信号の位相が 270° となるように収束して分周動作が得られる。図 4-12 から分 かるように、提案した分周器の出力電流  $i_{out}$ の振幅は、 $i_{cl}$ が存在するために従来よりも大き くなるため、ループ利得も大きくなる。即ち、消費電力を従来の分周器よりも低減できる。 高周波では、iclによるループ利得増大によって、従来の分周器よりも大きな電圧振幅が得ら れる。したがって負荷回路による位相シフトの許容量が従来よりも大きくなるため、高い周 波数まで分周動作させることが可能となる。しかしながら、提案した分周器は低い周波数に 動作の限界がある。低い周波数では負荷回路による位相シフトも小さいため、iclと imix の合 成電流である  $i_{out}$  の位相は  $270^\circ$  に近くなる必要がある。このような位相の  $i_{out}$  を得るには、  $i_{cl}$ と $i_{mix}$ の位相差が $180^{\circ}$ に近くなり、図 4-12に示すように合成電流が小さくなってしまう。 そのため、ループ利得が低下して分周動作ができなくなる。この問題は、シングル・バラン ス・ミキサの変換利得を増加させることで緩和できるため、ミキサの変換利得向上のための 検討を行った。

変換利得低下の原因の一つは、エミッタ結合ノードの寄生容量である。そこで、最小サイズのバイポーラ・トランジスタを用いるだけでなく、電流源回路に抵抗を用いた。この構成は、消費電力も低減できる。提案した分周器の開ループ利得の実部をシミュレーションにより求め、図 4-9 に実線で示した。従来の分周器との比較を公平に行うため、両者のバイアス電流、負荷抵抗、トランジスタサイズは等しくした。提案した分周器の 21.4 GHz におけるループ利得は 9.6 dB であり、従来に比べて 6.8 dB も大きくなることが分かった。5.3 dB 以上となる領域を分周動作周波数範囲とすると、8.0 GHz から 38.8 GHz の広い周波数範囲で分周動作が得られる見通しを得た。

# 4.3 測定結果

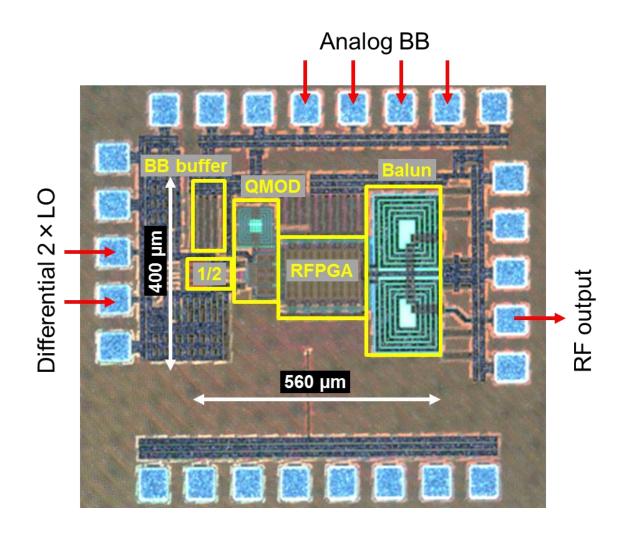

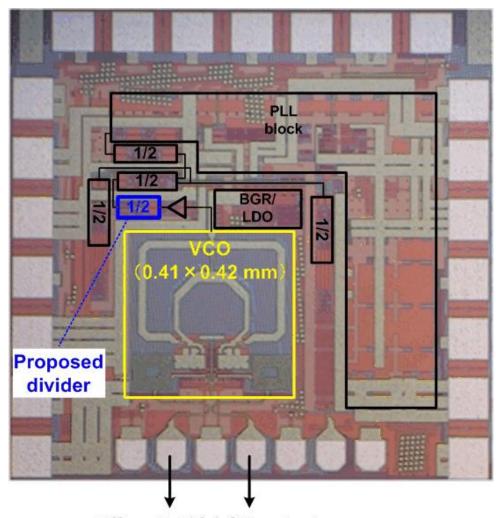

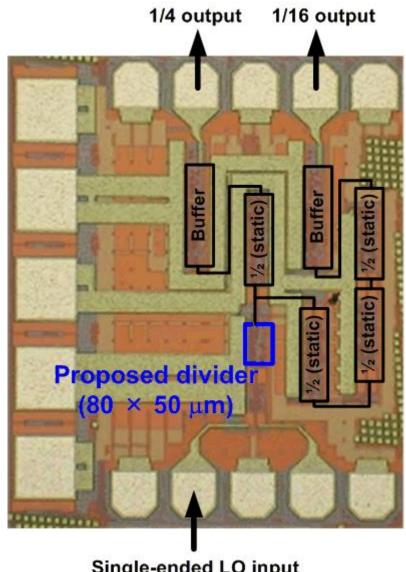

試作した 21.4 GHz シンセサイザチップのチップ写真を図 4-13 に示す。VCO のサイズは  $0.41 \times 0.42$  mm である。図 4-14 は分周器の特性を測定するためのテストチップである。提案した分周器のサイズは  $0.08 \times 0.05$  mm と非常に小さくすることができた。VCO および分周器の特性はオンウェハでプローブを用いて測定した。VCO と分周器の電源電圧は、それぞれ  $1.1 \text{ V } \ge 1.8 \text{ V }$  である。

Differential 21.4-GHz output

図 4-13 試作した周波数シンセサイザのチップ写真

Single-ended LO input

図 4-14 試作した周波数分周器のテストチップの写真

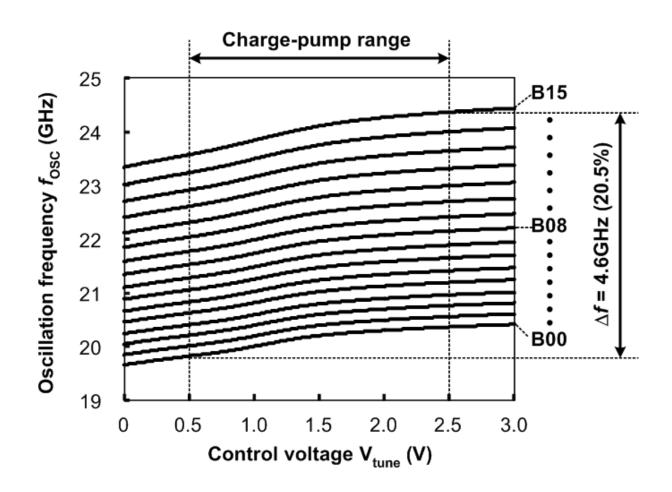

VCO の発振周波数制御特性を図 4-15 に示す。VCO は、容量バンクのビット状態を制御することで 16 の周波数バンド (B00 から B15) を設定でき、チャージポンプ回路の出力電圧範囲である  $0.5\,\mathrm{V}$  から  $2.5\,\mathrm{V}$  の微調整電圧 ( $V_\mathrm{tune}$ ) 範囲で、 $19.8\,\mathrm{GHz}$  から  $24.4\,\mathrm{GHz}$  の隙間のない広い周波数範囲で発振することを確認した。周波数可変範囲は  $4.6\,\mathrm{GHz}$  であり、中心周波数( $22.1\,\mathrm{GHz}$ )に対して 20.5% の周波数可変率となる。広い周波数可変範囲は、 $8.5\,\mathrm{C}$  が、 $8.5\,\mathrm{C}$  が、 $8.5\,\mathrm{C}$  に対して  $8.5\,\mathrm{C}$  が、 $8.5\,\mathrm{C}$  に対して  $8.5\,\mathrm{C}$  に対して  $8.5\,\mathrm{C}$  に対して  $8.5\,\mathrm{C}$  に対して  $8.5\,\mathrm{C}$  に対して  $8.5\,\mathrm{C}$  に固定した時の周波数粗調整範囲は  $8.6\,\mathrm{C}$  であり、図  $8.5\,\mathrm{C}$  に $8.5\,\mathrm{C}$  に固定した時の周波数粗調整範囲は  $8.6\,\mathrm{C}$  であり、図  $8.5\,\mathrm{C}$  に $8.5\,\mathrm{C}$  に固定した時の周波数れて  $8.5\,\mathrm{C}$  に固定した時の周波数

図 4-15 VCO の周波数制御特性の測定結果

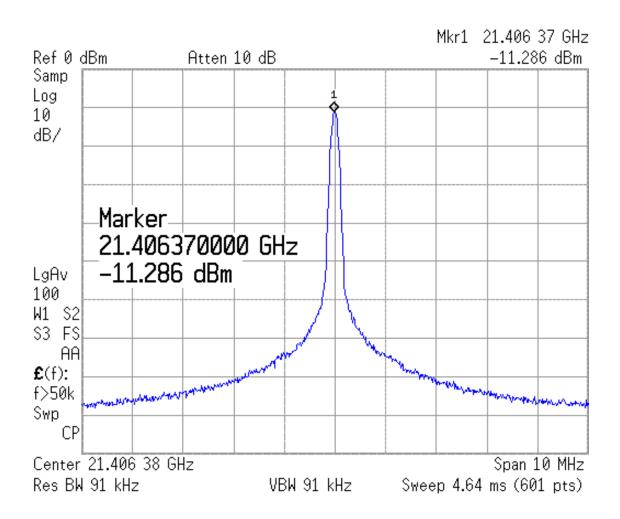

測定した 21.4 GHz のスペクトルを図 4-16 に示す。発振周波数の周辺に不要なスプリアス信号や雑音の重畳は観測されなかった。テスト用のバッファ回路を用いて出力しているため出力電力は参考値であるが、-11.3 dBm であり、位相雑音や発振周波数等の評価を行うには十分な大きさの出力が得られることを確認した。

図 4-16 VCO の出力スペクトルの測定結果

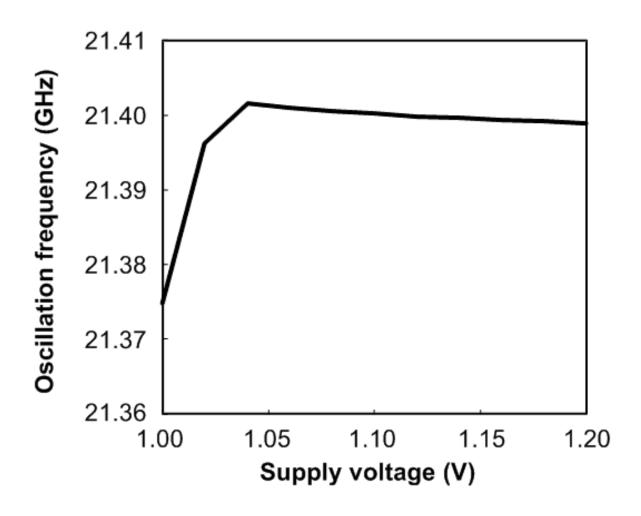

VCO 発振周波数の電源電圧プッシングの測定結果を図 4-17 に示す。電源電圧が 1.05 V以下では LDO の駆動トランジスタ (MP1) のオーバードライブ電圧が不足するため、非飽和領域となり電源電圧に対する感度が大きいが、1.05 V以上では MP1 が飽和領域で動作するため、非常に低いプッシング  $(-1.65~\mathrm{MHz/V})$  に抑圧されることを確認した。

図 4-17 VCO の電源電圧プッシングの測定結果

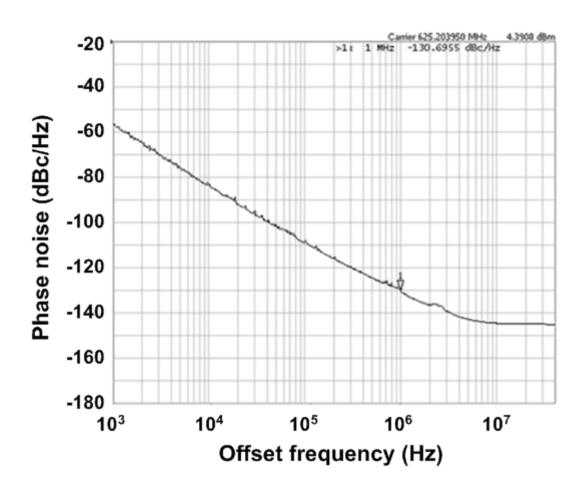

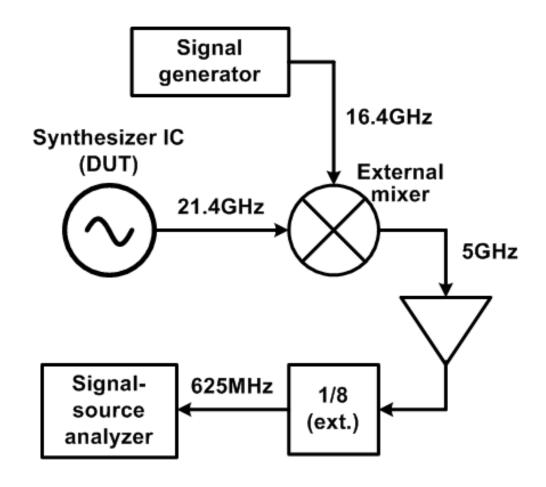

位相雑音スペクトルの測定結果を図 4-18 に示す。VCO 周波数バンドは B15 を、 $V_{\text{tune}}$  は 1.5 V に設定した。発振周波数は 24.1 GHz である。位相雑音の評価系を図 4-19 に示す。位相雑音はシグナル・ソース・アナライザ(SSA)を用いて測定したのであるが、SSA の入力上限周波数が 7 GHz であったため、24.1 GHz の信号を直接測定することができなかった。そこで、外部ミキサに用いて VCO 出力信号を 5 GHz の信号にダウンコンバートし、さらに 1/8 に分周して測定した。分周後の 1 MHz 離調時の位相雑音は-130.7 dBc/Hz であり、分周前に換算すると-112.6 dBc/Hz と良好な位相雑音特性が得られることを確認した。分周器の位相雑音は 1 MHz 離調時に-150 dBc/Hz 以下であり、測定結果の-130.7 dBc/Hz に対して 19.3 dB 以上低く、測定への影響は極めて少ない。

図 4-18 VCO の位相雑音特性の測定結果

図 4-19 VCO の位相雑音の測定系

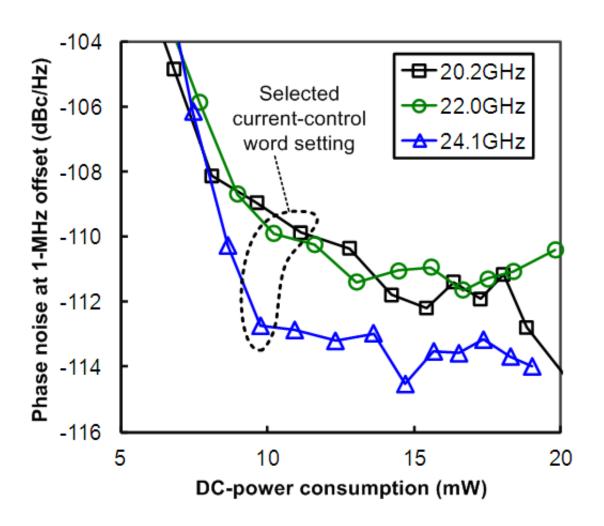

1MHz 離調時の位相雑音の消費電力依存性を図 4-20 に示す。 $V_{tune}$  は 1.5 V に設定した。図 4-20 の特性は、1/8 周波数分周による位相雑音改善分(約 18 dB)を補正して分周前の位相雑音に換算した値である。また、消費電力は電流制御ビットを変化させることで変化させており、LDO の消費電力(2.8 mW)も含んでいる。消費電力を増加させることで位相雑音は改善し、電流制御ビットを点線で囲った値にすることで、位相雑音は全バンドに渡って-112.6 dBc/Hz から-109.9 dBc/Hz の間に低く抑えられることを確認した。

図 4-20 VCO の 1MHz 離調時の位相雑音の消費電力依存性

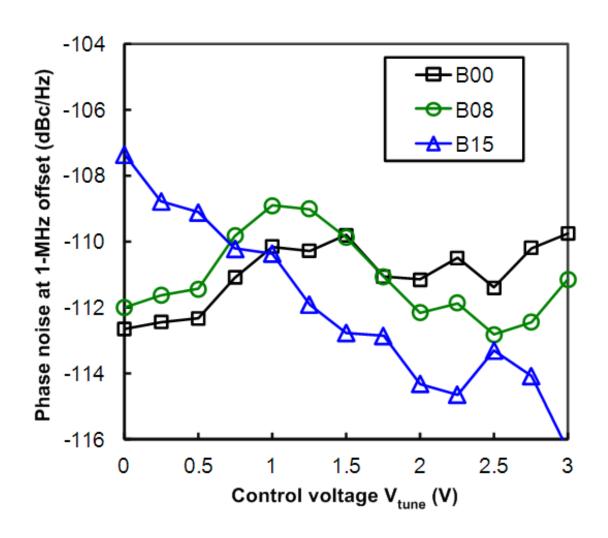

図 4-21 は、測定した 1 MHz 離調時の位相雑音の  $V_{tune}$  依存性である。図 4-20 と同様に、特性線が 3 本あるが、これらは設定した VCO バンドが異なり、発振周波数が異なる。チャージポンプ回路の出力電圧範囲である 0.5 から 2.5V の範囲で、位相雑音は-109.0 dBc/Hz であった。これら図 4-20 と図 4-21 に示した良好な位相雑音特性は、トランスフォーマの最適設計によるものである。

図 4-21 VCO の 1MHz 離調時の位相雑音の Vtune 依存性

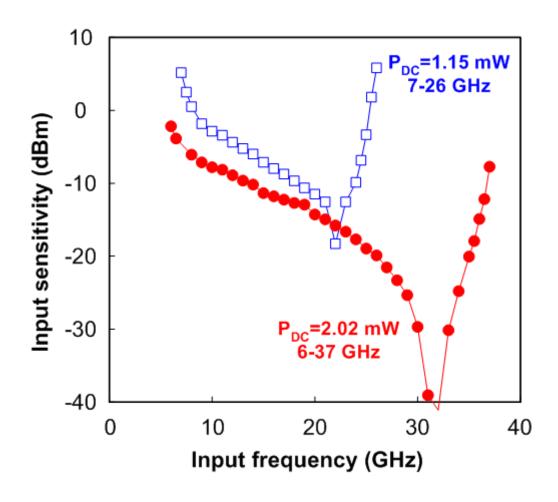

測定した分周器の入力感度を図 4-22 に示す。ここで分周器動作の定義は、不要信号なく所望の信号を出力できることとした。消費電力を 1.15 mW に設定したときには、所望の周波数である 21.4 GHz を含む 7 GHz から 26 GHz までの周波数範囲で分周動作が確認できた。さらに、消費電力を 2.02 mW まで増加すると、最大動作周波数は 37 GHz まで上昇することを確認した。この広い周波数範囲と低い消費電力の両立は、提案した分周器の構成によるものである。

図 4-22 分周器の入力感度の測定結果

VCO の測定結果を、他の発表のシリコンプロセスを用いた VCO (発振周波数: 28 GHz  $\sim$ 42 GHz) と比較した (表 4-1)。比較のため、以下の周波数可変範囲を考慮した VCO の性能指標 (Figure Of Merit) である  $FOM_T$ を用いた。

$$FOM_{T} = phn - 20\log\left(\frac{f_{OSC\_c}}{f_{offset}}\frac{FTR}{10}\right) + 10\log(P_{DC})$$

(4-1)

本研究の VCO は、-191.7~dBc/Hz の  $FOM_T$  を達成し、20~GHz 近傍の VCO では世界トップレベルである。また、分周器の測定結果も同様に比較した(表 4-2)。提案した分周器は、20~GHz 近傍のダイナミック分周器では最も広い動作範囲を達成した。

表 4-1 20GHz 帯 VCO の性能比較

| Ref.         | Technology          | Center frequency. | Frequency tuning range ratio to $f_{OSC\_c}$ | Phase noise @ offset freq. | DC-power dissipation | Figure of merit            |

|--------------|---------------------|-------------------|----------------------------------------------|----------------------------|----------------------|----------------------------|

|              |                     | $f_{ m OSC\_c}$   | FTR                                          | $phn@f_{offset}$           | $P_{\mathrm{DC}}$    | $FOM_{\mathrm{T}}^{}^{*}}$ |